## LVDS/Anything-to-LVPECL/LVDS Dual Translator

#### **General Description**

The MAX9376 is a fully differential, high-speed, LVDS/ anything-to-LVPECL/LVDS dual translator designed for signal rates up to 2GHz. One channel is LVDS/ anything-to-LVPECL translator and the other channel is LVDS/anything-to-LVDS translator. The MAX9376's extremely low propagation delay and high speed make it ideal for various high-speed network routing and backplane applications.

The MAX9376 accepts any differential input signal within the supply rails and with minimum amplitude of 100mV. Inputs are fully compatible with the LVDS, LVPECL, HSTL, and CML differential signaling standards. LVPECL outputs have sufficient current to drive  $50\Omega$  transmission lines. LVDS outputs conform to the ANSI EIA/TIA-644 LVDS standard.

The MAX9376 is available in a 10-pin  $\mu$ MAX® package and operates from a single +3.3V supply over the -40°C to +85°C temperature range.

## **Applications**

- Backplane Logic Standard Translation

- LVDS-to-LVPECL, LVPECL-to-LVDS Up/Downconverters

- LANs

- WANs

- DSLAMs

- DLCs

#### **Features**

- Guaranteed 2GHz Switching Frequency

- Accepts LVDS/LVPECL/Anything Inputs

- 421ps (typ) Propagation Delays

- 30ps (max) Pulse Skew

- 2ps<sub>RMS</sub> (max) Random Jitter

- Minimum 100mV Differential Input to Guarantee AC Specifications

- Temperature-Compensated LVPECL Output

- +3.0V to +3.6V Power-Supply Operating Range

- >2kV ESD Protection (Human Body Model)

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX9376EUB+ | -40°C to +85°C | 10 μMAX     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

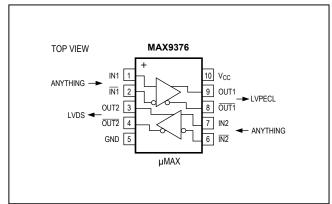

## **Pin Configuration**

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

## LVDS/Anything-to-LVPECL/LVDS Dual Translator

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND0.3V to +4.1V                   | Junction Temperature+150°C                  |

|-------------------------------------------------------|---------------------------------------------|

| Inputs (IN_, IN_)0.3V to (V <sub>CC</sub> + 0.3V)     | Storage Temperature Range65?C to +150°C     |

| IN to IN±3.0V                                         | ESD Protection                              |

| Continuous Output Current50mA                         | Human Body Model (IN_, ĪN_, OUT_, OUT_)≥2kV |

| Surge Output Current100mA                             | Soldering Temperature (10s)+300°C           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                             |

| 10-Pin μMAX (derate 5.6mW/°C above +70°C)444mW        |                                             |

| θ <sub>JA</sub> in Still Air (Note 1)+180°C/W         |                                             |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under ?Absolute Maximum Ratings? may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

$(V_{CC}$  = +3.0V to +3.6V, differential input voltage  $|V_{ID}|$  = 0.1V to 3.0V, input voltage  $(V_{IN}, V_{IN})$  = 0 to  $V_{CC}$ , input common-mode voltage  $V_{CM}$  = 0.05V to  $(V_{CC}$  - 0.05V), LVPECL outputs terminated with 50 $\Omega$  ±1% to  $(V_{CC}$  - 2.0V), LVDS outputs terminated with 100 $\Omega$  ±1%,  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.3V,  $|V_{ID}|$  = 0.2V, input common-mode voltage  $V_{CM}$  = 1.2V,  $T_A$  = +25°C, unless otherwise noted.) (Notes 2, 3, 4)

| DADAMETED                                                               | CVMDOL                               | CONDITIONS                                      |       | -40°C |                           | +25°C |       |                           | +85°C |                            |                           | UNITS |

|-------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|-------|-------|---------------------------|-------|-------|---------------------------|-------|----------------------------|---------------------------|-------|

| PARAMETER                                                               | SYMBOL                               |                                                 | MIN   | TYP   | MAX                       | MIN   | TYP   | MAX                       | MIN   | TYP                        | MAX                       | UNIIS |

| DIFFERENTIAL INPUTS (IN                                                 | _, ĪN_)                              |                                                 |       |       |                           |       |       |                           |       |                            |                           |       |

| Differential Input Threshold                                            | V <sub>THD</sub>                     |                                                 | -100  |       | +100                      | -100  |       | +100                      | -100  |                            | +100                      | mV    |

| Input Current                                                           | I <sub>IN</sub> ,<br>I <u>īN</u>     | $V_{IN}$ , $V_{\overline{IN}} = V_{CC}$ or $0V$ | -20   |       | +20                       | -20   |       | +20                       | -20   |                            | +20                       | μA    |

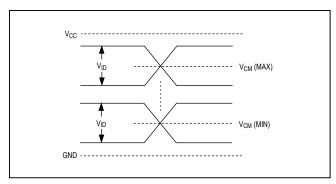

| Input Common-Mode<br>Voltage                                            | V <sub>CM</sub>                      | Figure 1                                        | 0.05  |       | V <sub>CC</sub> -<br>0.05 | 0.05  |       | V <sub>CC</sub> -<br>0.05 | 0.05  |                            | V <sub>CC</sub> -<br>0.05 | V     |

| LVPECL OUTPUTS (OUT1,                                                   | OUT1)                                |                                                 |       |       |                           |       |       |                           |       |                            |                           |       |

| Single-Ended Output High Voltage                                        | V <sub>OH</sub>                      | Figure 3                                        |       |       |                           |       |       |                           |       | V <sub>CC</sub> -<br>0.976 |                           | V     |

| Single-Ended Output Low Voltage                                         | V <sub>OL</sub>                      | Figure 3                                        |       |       |                           |       |       |                           |       | V <sub>CC</sub> -<br>1.681 |                           | V     |

| Differential Output Voltage                                             | V <sub>OH</sub> -<br>V <sub>OL</sub> | Figure 3                                        | 595   | 710   |                           | 595   | 710   |                           | 595   | 710                        |                           | mV    |

| LVDS OUTPUTS (OUT2, OU                                                  | JT2)                                 |                                                 |       |       |                           |       |       |                           |       |                            |                           |       |

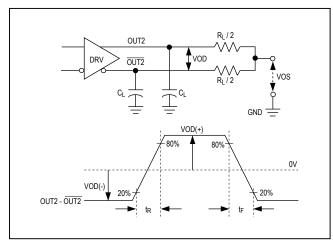

| Differential Output Voltage                                             | V <sub>OD</sub>                      | Figure 2                                        | 250   | 366   | 450                       | 250   | 352   | 450                       | 250   | 339                        | 450                       | mV    |

| Change in Magnitude<br>of VOD Between<br>Complementary Output<br>States | ΔV <sub>OD</sub>                     | Figure 2                                        |       | 1.0   | 20                        |       | 1.0   | 20                        |       | 1.0                        | 20                        | mV    |

| Offset Common-Mode<br>Voltage                                           | V <sub>OS</sub>                      | Figure 2                                        | 1.125 |       | 1.375                     | 1.125 | 1.250 | 1.375                     | 1.125 |                            | 1.375                     | V     |

| Change in Magnitude<br>of VOS Between<br>Complementary Output<br>States | ΔV <sub>OS</sub>                     | Figure 2                                        |       | 1.0   | 20                        |       | 1.0   | 20                        |       | 1.0                        | 20                        | mV    |

#### **DC Electrical Characteristics (continined)**

$(V_{CC}$  = +3.0V to +3.6V, differential input voltage  $|V_{ID}|$  = 0.1V to 3.0V, input voltage  $(V_{IN}, V_{IN})$  = 0 to  $V_{CC}$ , input common-mode voltage  $V_{CM}$  = 0.05V to  $(V_{CC}$  - 0.05V), LVPECL outputs terminated with 50 $\Omega$  ±1% to  $(V_{CC}$  - 2.0V), LVDS outputs terminated with 100 $\Omega$  ±1%,  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.3V,  $|V_{ID}|$  = 0.2V, input common-mode voltage  $V_{CM}$  = 1.2V,  $T_A$  = +25°C, unless otherwise noted.) (Notes 2, 3, 4)

| DADAMETED                                                        | SYMBOL          | CONDITIONS                                                                                                | -40°C |     | +25°C |     |     | +85°C |     |     | UNITS |       |

|------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|-----|-------|-----|-----|-------|-------|

| PARAMETER                                                        | STWBUL          | CONDITIONS                                                                                                | MIN   | TYP | MAX   | MIN | TYP | MAX   | MIN | TYP | MAX   | UNITS |

| Output Short-Circuit<br>Current, Either Output<br>Shorted to GND | I <sub>OS</sub> | V <sub>ID</sub> = ±100mV,<br>one output GND,<br>other output open<br>or shorted to<br>GND                 |       | 19  | 24    |     | 18  | 24    |     | 18  | 24    | mA    |

| Outputs Shorted Together   IOSAB                                 |                 | V <sub>ID</sub> = ±100mV,<br>V <sub>OUT</sub> _+ =<br>V <sub>OUT</sub>                                    |       | 4.0 | 12    |     | 4.0 | 12    |     | 4.0 | 12    | mA    |

| SUPPLY                                                           |                 | -                                                                                                         |       |     |       |     |     |       |     |     |       |       |

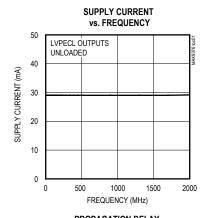

| Supply Current                                                   | I <sub>CC</sub> | All pins open except $V_{CC}$ and GND with LVDS outputs (OUT2, OUT2) loaded with differential $100\Omega$ |       | 24  | 40    |     | 29  | 40    |     | 31  | 40    | mA    |

#### **AC Electrical Characteristics**

$(V_{CC}$  = +3.0V to +3.6V, differential input voltage  $|V_{ID}|$  = 0.1V to 1.2V, input frequency  $\leq$  1.34GHz, differential input transition time = 125ps (20% to 80%), input voltage  $(V_{IN}, V_{IN})$  = 0 to  $V_{CC}$ , input common-mode voltage  $(V_{CM})$  = 0.05V to  $(V_{CC}$  - 0.05V), LVPECL outputs terminated with 50 $\Omega$  ±1% to  $(V_{CC}$  - 2.0V), LVDS outputs terminated with 100 $\Omega$  ±1%,  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.3V,  $|V_{ID}|$  = 0.2V, input common-mode voltage  $V_{CM}$  = 1.2V,  $T_A$  = +25°C, unless otherwise noted.) (Note 5)

| PARAMETER                                          | SYMBOL          | CONDITIONS                                | MIN | TYP | MAX | UNITS               |

|----------------------------------------------------|-----------------|-------------------------------------------|-----|-----|-----|---------------------|

| LVPECL OUTPUTS                                     |                 |                                           |     |     |     |                     |

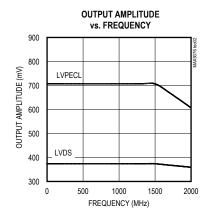

| Switching Frequency                                | fMAX            | V <sub>OH</sub> - V <sub>OL</sub> ≥ 250mV | 2.0 | 2.5 |     | GHz                 |

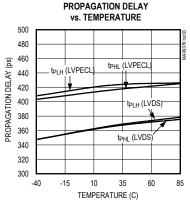

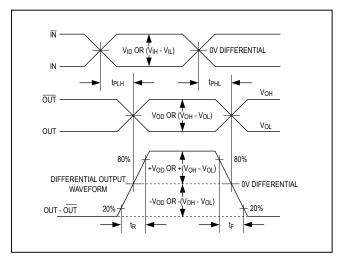

| Propagation Delay Low to High                      | tPLH            | Figure 3                                  | 250 | 421 | 600 | ps                  |

| Propagation Delay High to Low                      | tPHL            | Figure 3                                  | 250 | 421 | 600 | ps                  |

| Pulse Skew  t <sub>PLH</sub> - t <sub>PHL</sub>    | tSKEW           | Figure 3 (Note 6)                         |     | 6   | 30  | ps                  |

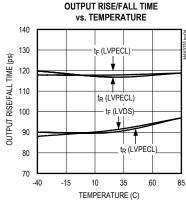

| Output Low-to-High Transition<br>Time (20% to 80%) | t <sub>R</sub>  | Figure 3                                  |     | 116 | 220 | ps                  |

| Output High-to-Low Transition<br>Time (20% to 80%) | tF              | Figure 3                                  |     | 119 | 220 | ps                  |

| Added Random Jitter                                | t <sub>RJ</sub> | f <sub>IN</sub> = 1.34GHz (Note 7)        |     | 0.7 | 2   | ps <sub>(RMS)</sub> |

| LVDS OUTPUTS                                       |                 |                                           |     |     |     |                     |

| Switching Frequency                                | fMAX            | V <sub>OD</sub> ≥ 250mV                   | 2.0 | 2.5 |     | GHz                 |

| Propagation Delay Low to High                      | tPLH            | Figure 3                                  | 250 | 363 | 600 | ps                  |

| Propagation Delay High to Low                      | tPHL            | Figure 3                                  | 250 | 367 | 600 | ps                  |

| Pulse Skew  t <sub>PLH</sub> - t <sub>PHL</sub>    | tSKEW           | Figure 3 (Note 6)                         |     | 5   | 30  | ps                  |

### **AC Electrical Characteristics (continued)**

$(V_{CC}$  = +3.0V to +3.6V, differential input voltage  $|V_{ID}|$  = 0.1V to 1.2V, input frequency  $\leq$  1.34GHz, differential input transition time = 125ps (20% to 80%), input voltage  $(V_{IN}, V_{IN})$  = 0 to  $V_{CC}$ , input common-mode voltage  $(V_{CM})$  = 0.05V to  $(V_{CC}$  - 0.05V), LVPECL outputs terminated with  $50\Omega$  ±1% to  $(V_{CC}$  - 2.0V), LVDS outputs terminated with  $100\Omega$  ±1%,  $T_A$  = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.3V,  $|V_{ID}|$  = 0.2V, input common-mode voltage  $V_{CM}$  = 1.2V,  $T_A$  = +25°C, unless otherwise noted.) (Note 5)

| PARAMETER                                          | SYMBOL         | CONDITIONS                         | MIN | TYP | MAX | UNITS               |

|----------------------------------------------------|----------------|------------------------------------|-----|-----|-----|---------------------|

| Output Low-to-High Transition<br>Time (20% to 80%) | <sup>t</sup> R | Figure 2                           |     | 93  | 220 | ps                  |

| Output High-to-Low Transition<br>Time (20% to 80%) | tF             | Figure 2                           |     | 91  | 220 | ps                  |

| Added Random Jitter                                | tRJ            | f <sub>IN</sub> = 1.34GHz (Note 7) |     | 0.8 | 2   | ps <sub>(RMS)</sub> |

- Note 2: Measurements are made with the device in thermal equilibrium. All voltages are referenced to ground except  $V_{THD}$ ,  $V_{ID}$ ,  $V_{OD}$ , and  $\Delta V_{OD}$ .

- Note 3: Current into a pin is defined as positive. Current out of a pin is defined as negative.

- **Note 4:** DC parameters production tested at T<sub>A</sub> = +25°C and guaranteed by design and characterization over the full operating temperature range.

- Note 5: Guaranteed by design and characterization, not production tested. Limits are set at ±6 sigma.

- Note 6: t<sub>SKEW</sub> is the magnitude difference of differential propagation delays for the same output under same conditions; t<sub>SKEW</sub> = |t<sub>PHL</sub> t<sub>PLH</sub>|.

- Note 7: Device jitter added to the input signal.

## **Typical Operating Characteristics**

$(V_{CC}$  = +3.3V, differential input voltage  $|V_{ID}|$  = 0.2V,  $V_{CM}$  = 1.2V, input frequency = 500MHz, LVPECL outputs terminated with 50 $\Omega$  ±1% to  $V_{CC}$  - 2.0V, LVDS outputs terminated with 100 $\Omega$  ±1%,  $T_A$  = +25°C, unless otherwise noted.)

#### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                         |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN1             | Differential LVDS/Anything Noninverting Input 1                                                                                                                                                                  |

| 2   | ĪN1             | Differential LVDS/Anything Inverting Input 1                                                                                                                                                                     |

| 3   | OUT2            | Differential LVDS Noninverting Output 2. Terminate with 100Ω ±1% to OUT2.                                                                                                                                        |

| 4   | OUT2            | Differential LVDS Inverting Output 2. Terminate with 100Ω ±1% to OUT2.                                                                                                                                           |

| 5   | GND             | Ground                                                                                                                                                                                                           |

| 6   | ĪN2             | Differential LVDS/Anything Inverting Input 2                                                                                                                                                                     |

| 7   | IN2             | Differential LVDS/Anything Noninverting Input 2                                                                                                                                                                  |

| 8   | OUT1            | Differential LVPECL Inverting Output. Terminate with 50 $\Omega$ ±1% to V <sub>CC</sub> - 2V.                                                                                                                    |

| 9   | OUT1            | Differential LVPECL Noninverting Output. Terminate with 50Ω ±1% to V <sub>CC</sub> - 2V.                                                                                                                         |

| 10  | V <sub>CC</sub> | Positive Supply. Bypass from $V_{CC}$ to GND with $0.1\mu F$ and $0.01\mu F$ ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device. |

## **Detailed Description**

The MAX9376 is a fully differential, high-speed, LVDS/ anything-to-LVPECL/LVDS dual translator designed for signal rates up to 2GHz. One channel is LVDS/ anything-to-LVPECL translator and the other channel is LVDS/anything-to-LVDS translator. The MAX9376's extremely low propagation delay and high speed make it ideal for various high-speed network routing and backplane applications.

The MAX9376 accepts any differential input signal within the supply rails and with a minimum amplitude of 100mV. Inputs are fully compatible with the LVDS, LVPECL, HSTL, and CML differential signaling standards. LVPECL outputs have sufficient current to drive  $50\Omega$  transmission lines. LVDS outputs conform to the ANSI EIA/TIA-644 LVDS standard.

#### Inputs

Inputs have a wide common-mode range of 0.05V to  $V_{CC}$  - 0.05V, which accommodates any differential signals within rails, and requires a minimum of 100mV to switch the outputs. This allows the MAX9376 inputs to support virtually any differential signaling standard.

#### **LVPECL Outputs**

The MAX9376 LVPECL outputs are emitter followers that require external resistive paths to a voltage source ( $V_T = V_{CC} - 2.0V$  typ) more negative than worst-case  $V_{OL}$  for proper static and dynamic operation. When properly terminated, the outputs generate steady-state voltage levels,  $V_{OL}$  or  $V_{OH}$  with fast transition edges between state levels. Output current always flows into the termination during proper operation.

#### LVDS Outputs

The MAX9376 LVDS outputs require a resistive load to terminate the signal and complete the transmission loop. Because the device switches current and not voltage, the actual output voltage swing is determined by the value of the termination resistor. With a 3.5mA typical output current, the MAX9376 produces an output voltage of 350mV when driving a  $100\Omega$  load.

Figure 1. Input Definition

Figure 2. LVDS Output Load and Transition Times

Figure 3. Differential Input-to-Output Propagation Delay Timing Diagram

## **Applications Information**

#### **LVPECL Output Termination**

Terminate the MAX9376 LVPECL outputs with  $50\Omega$  to (V<sub>CC</sub> - 2V) or use equivalent Thevenin terminations. Terminate OUT1 and  $\overline{\text{OUT1}}$  with identical termination on each for low output distortion. When a single-ended signal is taken from the differential output, terminate both OUT1 and  $\overline{\text{OUT1}}$ .

Ensure that output currents do not exceed the current limits as specified in the *Absolute Maximum Ratings*. Under all operating conditions, the device's total thermal limits should be observed.

#### **LVDS Output Termination**

The MAX9376 LVDS outputs are current-steering devices; no output voltage is generated without a termination resistor. The termination resistors should match the differential impedance of the transmission line. Output voltage levels are dependent upon the value of the termination resistor. The MAX9376 is optimized for point-to-point interface with  $100\Omega$  termination resistors at the receiver inputs. Termination resistance values may range between  $90\Omega$  and  $132\Omega$ , depending on the characteristic impedance of the transmission medium.

#### Supply Bypassing

Bypass  $V_{CC}$  to ground with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.01\mu F$  capacitors. Place the capacitors as close to the device as possible with the  $0.01\mu F$  capacitor closest to the device pins.

#### **Traces**

Circuit board trace layout is very important to maintain the signal integrity of high-speed differential signals. Maintaining integrity is accomplished in part by reducing signal reflections and skew, and increasing common-mode noise immunity.

Signal reflections are caused by discontinuities in the  $50\Omega$  characteristic impedance of the traces. Avoid discontinuities by maintaining the distance between differential traces, not using sharp corners or using vias. Maintaining distance between the traces also increases common-mode noise immunity. Reducing signal skew is accomplished by matching the electrical length of the differential traces.

### MAX9376

# LVDS/Anything-to-LVPECL/LVDS Dual Translator

## **Chip Information**

PROCESS: Bipolar

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE CODE | DOCUMENT NO. |

|-----------------|--------------|--------------|

| 10µMAX          | U10+2        | 21-0061      |

## MAX9376

## LVDS/Anything-to-LVPECL/LVDS Dual Translator

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                               | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------|------------------|

| 0                  | 4/03             | Initial release                                           |                  |

| 1                  | 10/09            | Updated Ordering Information and Absolute Maximum Ratings | 1, 2             |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX9376EUB+ MAX9376EUB+T