#### **General Description**

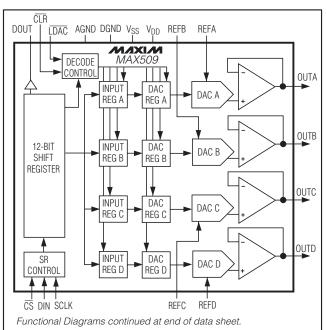

The MAX509/MAX510 are quad, serial-input, 8-bit voltage-output digital-to-analog converters (DACs). They operate with a single +5V supply or dual ±5V supplies. Internal, precision buffers swing rail-to-rail. The reference input range includes both supply rails.

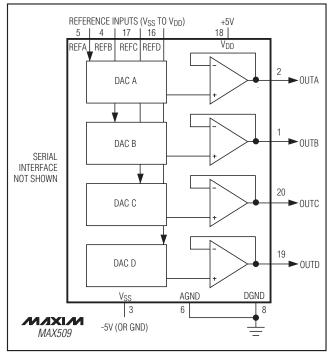

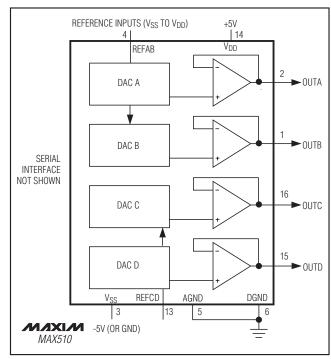

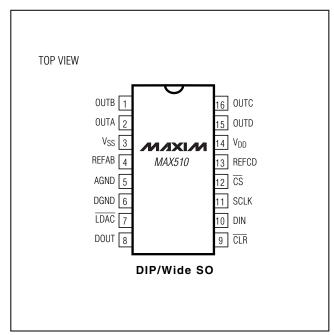

The MAX509 has four separate reference inputs, allowing each DAC's full-scale range to be set independently. 20-pin DIP, SSOP, and SO packages are available. The MAX510 is identical to the MAX509 except it has two reference inputs, each shared by two DACs. The MAX510 is housed in space-saving 16-pin DIP and SO packages.

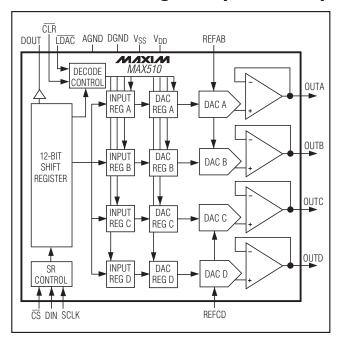

The serial interface is double-buffered: A 12-bit input shift register is followed by four 8-bit buffer registers and four 8-bit DAC registers. A 12-bit serial word is used to load data into each register. Both input and DAC registers can be updated independently or simultaneously with single software commands. Two additional asynchronous control pins provide simultaneous updating (LDAC) or clearing (CLR) of input and DAC registers.

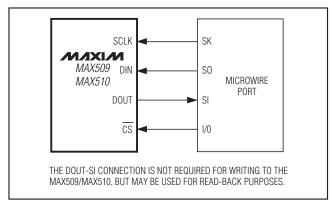

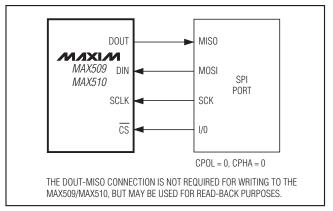

The interface is compatible with MICROWIRETM and SPI/QSPI<sup>TM</sup>. All digital inputs and outputs are TTL/CMOS compatible. A buffered data output provides for readback or daisy-chaining of serial devices.

#### **Features**

- ♦ Single +5V or Dual ±5V Supply Operation

- ♦ Output Buffer Amplifiers Swing Rail-to-Rail

- ♦ Reference Input Range Includes Both Supply Rails

- ♦ Calibrated Offset, Gain, and Linearity (1LSB TUE)

- 10MHz Serial Interface, Compatible with SPI, QSPI (CPOL = CPHA = 0) and MICROWIRE

- ♦ Double-Buffered Registers for Synchronous **Updating**

- ♦ Serial Data Output for Daisy-Chaining

- **Power-On Reset Clears Serial Interface and Sets** All Registers to Zero

#### Ordering Information

| PART        | TEMP RANGE   | PIN-PACKAGE | TUE<br>(LSB) |

|-------------|--------------|-------------|--------------|

| MAX509ACPP+ | 0°C to +70°C | 20 PDIP     | ±1           |

| MAX509BCPP+ | 0°C to +70°C | 20 PDIP     | ±1.5         |

| MAX509ACWP+ | 0°C to +70°C | 20 Wide SO  | ±1           |

| MAX509BCWP+ | 0°C to +70°C | 20 Wide SO  | ±1.5         |

| MAX509ACAP+ | 0°C to +70°C | 20 SSOP     | ±1           |

#### Ordering Information continued on last page.

\*\*Contact factory for availability and processing to MIL-STD-883. +Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Functional Diagrams**

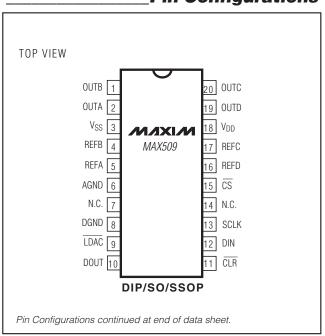

#### Pin Configurations

MICROWIRE is a trademark of National Semiconductor Corp. SPI and QSPI are trademarks of Motorola.

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND             | 0.3V, +6V                         |

|-------------------------------------|-----------------------------------|

| V <sub>DD</sub> to AGND             | 0.3V, +6V                         |

| V <sub>SS</sub> to DGND             | 6V, +0.3V                         |

| V <sub>SS</sub> to AGND             | 6V, +0.3V                         |

| V <sub>DD</sub> to V <sub>S</sub> S | 0.3V, +12V                        |

| Digital Input Voltage to DGND       | 0.3V, (V <sub>DD</sub> + 0.3V)    |

| REF                                 |                                   |

| OUT                                 | V <sub>DD</sub> , V <sub>SS</sub> |

| Maximum Current into Any Pin        | 50mA                              |

| Continuous Power Dissipation (TA =  | : +70°C)                          |

| 16-Pin Plastic DIP (derate 10.53mW  | //°C above +70°C)842mW            |

| 16-Pin Wide SO (derate 9.52mW/°C    | above +70°C)762mW                 |

| 16-Pin CERDIP (derate 10.00mW/°C    | C above +70°C)800mW               |

|                                     |                                   |

| 20-Pin Plastic DIP (derate 11.11mW/°C above +70°C)889mW |

|---------------------------------------------------------|

| 20-Pin Wide SO (derate 10.00mW/°C above +70°C)800mW     |

| 20-Pin SSOP (derate 10.00mW/°C above +70°C)800mW        |

| 20-Pin CERDIP (derate 11.11mW/°C above +70°C)889mW      |

| Operating Temperature Ranges:                           |

| MAX5C0°C to +70°C                                       |

| MAX5E40°C to +85°C                                      |

| MAX5MJ55°C to +125°C                                    |

| Storage Temperature Range65°C to +150°C                 |

| Lead Temperature (soldering, 10s)+300°C                 |

| Soldering Temperature (reflow)                          |

Lead (Pb)-free packages .....+260°C

Packages containing lead (Pb) .....+260°C

**Note:** The outputs may be shorted to V<sub>DD</sub>, V<sub>SS</sub>, or AGND if the package power dissipation is not exceeded. Typical short-circuit current to AGND is 50mA. Do not bias AGND more than +1V above DGND, or more than 2.5V below DGND.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V \pm 10\%, V_{SS} = 0V \text{ to } -5.5V, V_{REF} = 4V, AGND = DGND = 0V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$

| PARAMETER                                   | SYMBOL | CONDITION                                                               | S     | MIN | TYP | MAX  | UNITS |  |

|---------------------------------------------|--------|-------------------------------------------------------------------------|-------|-----|-----|------|-------|--|

| STATIC ACCURACY                             |        |                                                                         | '     |     |     |      |       |  |

| Resolution                                  |        |                                                                         |       | 8   |     |      | Bits  |  |

|                                             |        | VREF = +4V,                                                             | MAX5A |     |     | ±1   |       |  |

| Total Unadjusted From                       | TUE    | $V_{SS} = 0V \text{ or } -5V \pm 10\%$                                  | MAX5B |     |     | ±1.5 | LSB   |  |

| Total Unadjusted Error                      | IUE    | VREF = -4V,                                                             | MAX5A |     |     | ±1   |       |  |

|                                             |        | $V_{SS} = -5V \pm 10\%$                                                 | MAX5B |     |     | ±1.5 |       |  |

| Differential Nonlinearity                   | DNL    | Guaranteed monotonic                                                    |       |     |     | ±1   | LSB   |  |

|                                             |        | 0 1 001                                                                 | MAX5C |     |     | 14   |       |  |

|                                             |        | Code = 00 hex,<br>$V_{SS} = 0V$                                         | MAX5E |     |     | 16   | – mV  |  |

| Zara Cada Frrar                             | ZCE    | 122 - 01                                                                | MAX5M |     |     | 20   |       |  |

| Zero-Code Error                             | ZCE    | 0 1 001                                                                 | MAX5C |     |     | ±14  |       |  |

|                                             |        | Code = 00 hex,<br>$V_{SS} = -5V \pm 10\%$                               | MAX5E |     |     | ±16  |       |  |

|                                             |        |                                                                         | MAX5M |     |     | ±20  |       |  |

| Zero-Code-Error Supply Rejection            |        | Code = 00 hex, V <sub>DD</sub> = 5V<br>V <sub>SS</sub> = 0V or -5V ±10% | ±10%, |     | 1   | 2    | mV    |  |

| Zero-Code<br>Temperature Coefficient        |        | Code = 00 hex                                                           |       |     | ±10 |      | μV/°C |  |

| Full-Scale Error                            |        | Code = FF hex                                                           |       |     |     | ±14  | mV    |  |

|                                             |        | Code = FF hex,                                                          | MAX5C |     | 1   | 4    |       |  |

| Full-Scale-Error Supply Rejection           |        | $V_{DD} = +5V \pm 10\%,$                                                | MAX5E |     | 1   | 8    | mV    |  |

|                                             |        | $V_{SS} = 0V \text{ or } -5V \pm 10\%$                                  | MAX5M |     | 1   | 12   | 1     |  |

| Full-Scale-Error<br>Temperature Coefficient |        | Code = FF hex                                                           |       |     | ±10 |      | μV/°C |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +5V \pm 10\%, V_{SS} = 0V \text{ to -5.5V}, V_{REF} = 4V, AGND = DGND = 0V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted.)$

| PARAMETER                          | SYMBOL          | CONDITIONS                                                     | 3        | MIN                   | TYP | MAX             | UNITS             |

|------------------------------------|-----------------|----------------------------------------------------------------|----------|-----------------------|-----|-----------------|-------------------|

| REFERENCE INPUTS                   |                 |                                                                |          |                       |     |                 |                   |

| Input Voltage Range                |                 |                                                                |          | V <sub>SS</sub>       |     | V <sub>DD</sub> | V                 |

| Input Desistance (Note 1)          |                 | Code FF how                                                    | MAX509   | 16                    | 24  |                 | 1.0               |

| Input Resistance (Note 1)          |                 | Code = 55 hex                                                  | MAX510   | 8                     | 12  |                 | kΩ                |

|                                    |                 | 0 1 001                                                        | MAX509   |                       | 15  |                 | _                 |

| Input Capacitance (Note 2)         |                 | Code = 00 hex                                                  | MAX510   |                       | 30  |                 | - pF              |

| Channel-to-Channel Isolation       |                 | (Note 3)                                                       | -1       |                       | -60 |                 | dB                |

| AC Feedthrough                     |                 | (Note 4)                                                       |          |                       | -70 |                 | dB                |

| DAC OUTPUTS                        |                 |                                                                |          |                       |     |                 |                   |

| Full-Scale Output Voltage          |                 |                                                                |          | V <sub>SS</sub>       |     | V <sub>DD</sub> | V                 |

|                                    |                 | VREF = 4V, load regulation                                     | ≤ 1/4LSB | 2                     |     |                 |                   |

|                                    |                 | VREF = -4V, $V_{SS}$ = -5V ±10%, load regulation $\leq$ 1/4LSB |          | 2                     |     |                 |                   |

| Resistive Load                     |                 | VREF = V <sub>DD</sub> MAX5C/E,<br>load regulation ≤ 1LSB      | 10       |                       |     | kΩ              |                   |

|                                    |                 | VREF = V <sub>DD</sub> MAX5M,<br>load regulation ≤ 2LSB        |          | 10                    |     |                 |                   |

| DIGITAL INPUTS                     |                 |                                                                |          |                       |     |                 |                   |

| Input High Voltage                 | VIH             |                                                                |          | 2.4                   |     |                 | V                 |

| Input Low Voltage                  | VIL             |                                                                |          |                       |     | 0.8             | V                 |

| Input Current                      | I <sub>IN</sub> | $V_{IN} = 0V \text{ or } V_{DD}$                               |          |                       |     | 1.0             | μΑ                |

| Input Capacitance                  | CIN             | (Note 5)                                                       |          |                       |     | 10              | рF                |

| DIGITAL OUTPUTS                    | l               |                                                                |          |                       |     |                 |                   |

| Output High Voltage                | VoH             | ISOURCE = 0.2mA                                                |          | V <sub>DD</sub> - 0.5 |     |                 | V                 |

| Output Low Voltage                 | Vol             | ISINK = 1.6mA                                                  |          |                       |     | 0.4             | V                 |

| DYNAMIC PERFORMANCE                |                 | 1                                                              |          |                       |     |                 |                   |

|                                    |                 |                                                                | MAX5C    | 1.0                   |     |                 |                   |

| Voltage-Output Slew Rate           |                 | Positive and negative                                          | MAX5E    | 0.7                   |     |                 | V/µs              |

|                                    |                 |                                                                | MAX5M    | 0.5                   |     |                 | 1                 |

| Output Settling Time (Note 6)      |                 | To 1/2LSB, 10kΩ II 100pF I                                     | oad      |                       | 6   |                 | μs                |

| Digital Feedthrough                |                 | Code = 00 hex, all digital in from 0V to V <sub>DD</sub>       | nputs    |                       | 5   |                 | nV-s              |

| Digital-to-Analog Glitch Impulse   |                 | Code 128→127                                                   |          | 12                    |     | nV-s            |                   |

| Signal-to-Noise + Distortion Ratio | SINAD           | $VREF = 4V_{p-p}$ at 1kHz, $V_{DD}$ code = FF hex              | ) = 5V,  |                       | 87  |                 | dB                |

|                                    |                 | VREF = 4V <sub>p-p</sub> at 20kHz, V <sub>S</sub>              |          |                       | 74  |                 | 1                 |

| Multiplying Bandwidth              |                 | VREF = 0.5V <sub>p-p</sub> , 3dB band                          | width    |                       | 1   |                 | MHz               |

| Wideband Amplifier Noise           |                 |                                                                |          |                       | 60  |                 | μV <sub>RMS</sub> |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +5V \pm 10\%, V_{SS} = 0V \text{ to -5.5V}, V_{REF} = 4V, \text{AGND} = \text{DGND} = 0V, R_L = 10k\Omega, C_L = 100pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{unless otherwise noted.})$

| PARAMETER                | SYMBOL          | CONDITION                                               | IS      | MIN | TYP | MAX | UNITS |

|--------------------------|-----------------|---------------------------------------------------------|---------|-----|-----|-----|-------|

| POWER SUPPLIES           |                 |                                                         |         |     |     |     |       |

| Positive Supply Voltage  | V <sub>DD</sub> | For specified performance                               | 4.5     |     | 5.5 | V   |       |

| Negative Supply Voltage  | V <sub>SS</sub> | For specified performance                               | -5.5    |     | 0   | V   |       |

| Positive Supply Current  | IDD             | Outputs unloaded, all                                   | MAX5C/E |     | 5   | 10  | mA    |

| 1 Ositive Supply Current |                 | digital inputs = 0V or V <sub>DD</sub>                  | MAX5M   |     | 5   | 12  | IIIA  |

| Negative Supply Current  | Iss             | $V_{SS} = -5V \pm 10\%$ , outputs unloaded, all digital | MAX5C/E |     | 5   | 10  | mA    |

| Negative Supply Current  | 188             | inputs = 0V or V <sub>DD</sub>                          | MAX5M   |     | 5   | 12  |       |

- Note 1: Input resistance is code dependent. The lowest input resistance occurs at code = 55 hex.

- Note 2: Input capacitance is code dependent. The highest input capacitance occurs at code = 00 hex.

- **Note 3:** VREF = 4V<sub>p-p</sub>, 10kHz. Channel-to-channel isolation is measured by setting the code of one DAC to FF hex and setting the code of all other DACs to 00 hex.

- **Note 4:** VREF =  $4V_{p-p}$ , 10kHz. DAC code = 00 hex.

- Note 5: Guaranteed by design.

- Note 6: Output settling time is measured by taking the code from 00 hex to FF hex, and from FF hex to 00 hex.

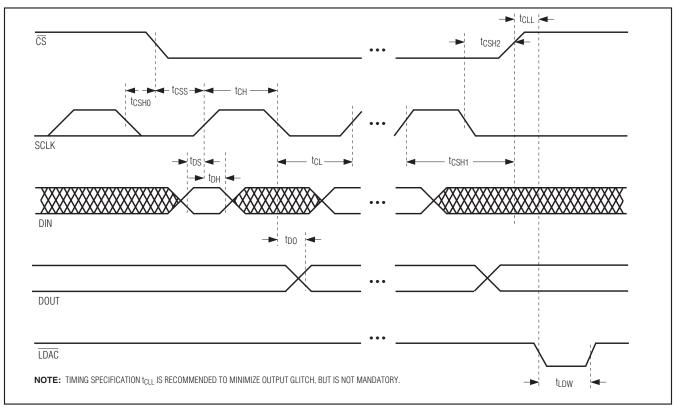

#### **TIMING CHARACTERISTICS**

$(V_{DD} = +5V \pm 10\%, V_{SS} = 0V \text{ to -5V}, V_{REF} = 4V, AGND = DGND = 0V, C_L = 50pF, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted.)$

| PARAMETER                       | SYMBOL          | CONDITIONS   | MIN | TYP | MAX  | UNITS |  |

|---------------------------------|-----------------|--------------|-----|-----|------|-------|--|

| LDAC Pulse Width Low            | t. 5            | MAX5C/E      | 40  | 20  |      |       |  |

| LDAC Pulse Width Low            | tldw            | MAX5M        | 50  | 25  |      | ns    |  |

| CS Rise to LDAC Fall Setup Time | tCLL            | (Notes 7, 8) | 0   |     |      | ns    |  |

| OLD Dule - Mielale I            |                 | MAX5C/E      | 40  | 20  |      |       |  |

| CLR Pulse Width Low             | tclw            | MAX5M        | 50  | 25  |      | ns    |  |

| SERIAL INTERFACE TIMING         |                 | ,            | ı   |     |      |       |  |

| CC Fall to CCL // Catura Time   | tooo            | MAX5C/E      | 40  |     |      | no    |  |

| CS Fall to SCLK Setup Time      | tcss            | MAX5M        | 50  |     |      | ns    |  |

| SCLK Fall to CS Rise Hold Time  | tCSH2           |              | 0   |     |      | ns    |  |

| SCLK Rise to CS Rise Hold Time  | tCSH1           | (Note 9)     | 40  |     |      | ns    |  |

| SCLK Fall to CS Fall Hold Time  | tcsH0           | (Note 7)     | 0   |     |      | ns    |  |

| DIN to SCLK Rise Setup Time     | tpo             | MAX5C/E      | 40  |     |      | ns    |  |

| DIN to Social file              | t <sub>DS</sub> | MAX5M        | 50  |     |      | 113   |  |

| DIN to SCLK Rise Hold Time      | tDH             |              | 0   |     |      | ns    |  |

| CCLV Clock Fraguency            | form            | MAX5C/E      |     | 20  | 12.5 | MHz   |  |

| SCLK Clock Frequency            | fclk            | MAX5M        |     | 20  | 10   | IVITZ |  |

| CCLI/ Dulas Width Lligh         | tou             | MAX5C/E      | 40  |     |      |       |  |

| SCLK Pulse Width High           | tch             | MAX5M        | 50  |     |      | ns    |  |

| CCLI/ Dulgo Width Low           | to              | MAX5C/E 40   |     |     |      |       |  |

| SCLK Pulse Width Low            | tCL             | MAX5M        | 50  |     |      | ns    |  |

| SCLK to DOUT Valid              | tpo             | MAX5C/E      | 10  |     | 100  |       |  |

| SCLINIO DOOT VAIID              | tDO             | MAX5M        | 10  |     | 100  | ns    |  |

Note 7: Guaranteed by design.

Note 8: If LDAC is activated prior to CS's rising edge, it must stay low for tLDW or longer after CS goes high.

**Note 9:** Minimum delay from 12th clock cycle to  $\overline{CS}$  rise.

# MAX509/MAX51

### **Quad, Serial 8-Bit DACs** with Rail-to-Rail Outputs

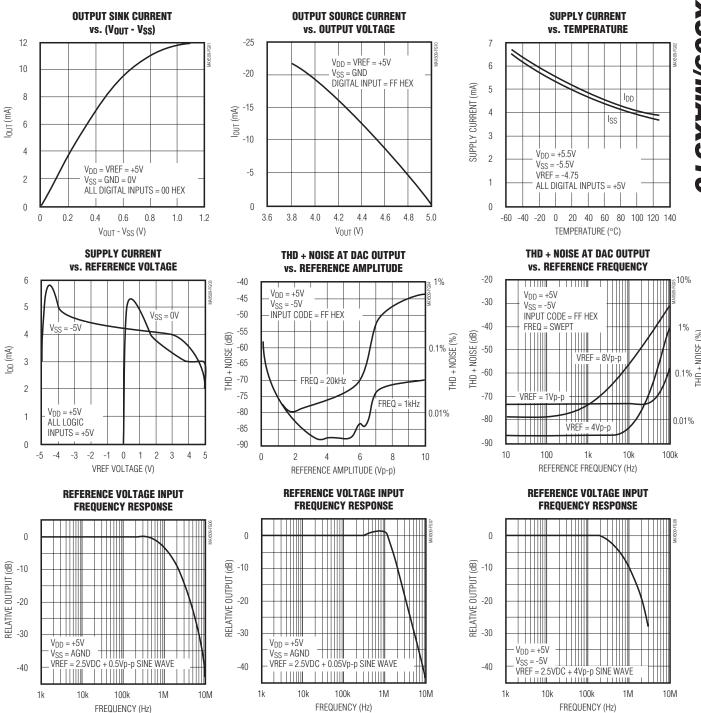

#### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

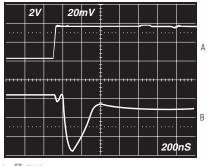

#### **WORST-CASE 1LSB DIGITAL STEP CHANGE**

A =  $\overline{\text{CS}}$ , 2V/div B = 0UTA, 20mV  $^{\sim}$ TIMEBASE = 200ns/div

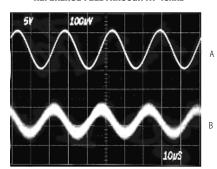

#### REFERENCE FEEDTHROUGH AT 40kHz

$\begin{array}{l} A = REFA, \ 10V_{p-p} \\ B = OUTA, \ 100\mu V/div, \ UNLOADED \\ TIMEBASE = 10\mu s/div \\ V_{DD} = +5V, \ V_{SS} = -5V \\ CODE = ALL \ 0s \end{array}$

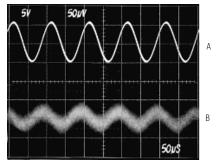

#### REFERENCE FEEDTHROUGH AT 10kHz

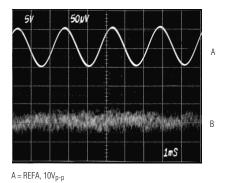

$$\begin{split} & \text{A} = \text{REFA, } 10\text{V}_{\text{p-p}} \\ & \text{B} = \text{OUTA, } 50\mu\text{V/div, UNLOADED} \\ & \text{TIMEBASE} = 50\mu\text{s/div} \end{split}$$

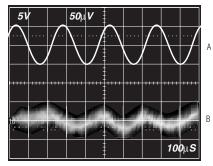

#### REFERENCE FEEDTHROUGH AT 4kHz

$$\begin{split} & A = REFA, \ 10V_{p-p} \\ & B = OUTA, \ 50\mu V/div, \ UNLOADED \\ & TIMEBASE = 100\mu s/div \end{split}$$

#### REFERENCE FEEDTHROUGH AT 400Hz

A = REFA, 10V<sub>p-p</sub> B = OUTA, 50μV/div, UNLOADED TIMEBASE = 1ms/div

#### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### **CLOCK FEEDTHROUGH**

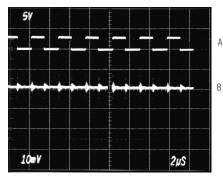

$A = SCLK, 333kHz \\ B = OUT\_, 10mV/div \\ TIMEBASE = 2\mu s/div$

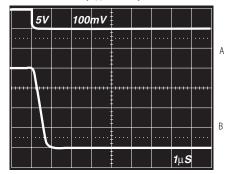

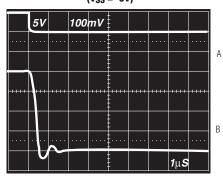

#### NEGATIVE SETTLING TIME (VSS = AGND)

A = DIGITAL INPUT, 5V/div B = OUT\_ , 2V/div TIMEBASE =  $1\mu$ s/div  $V_{DD}$  = +5V REF\_ = +4V ALL BITS ON TO ALL BITS OFF

$R_L=10k\Omega,\; C_L=100pF$

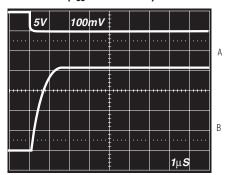

#### POSITIVE SETTLING TIME (Vss = AGND OR -5V)

$$\begin{split} & A = DIGITAL\ INPUT,\ 5V/div \\ & B = OUT\_\ ,\ 2V/div \\ & TIMEBASE = 1\mu s/div \\ & V_{DD} = +5V \\ & REF\_ = +4V \\ & ALL\ BITS\ OFF\ TO\ ALL\ BITS\ ON \\ & R_L = 10k\Omega,\ C_L = 100pF \end{split}$$

#### NEGATIVE SETTLING TIME (V<sub>SS</sub> = -5V)

A = DIGITAL INPUT, 5V/div B = OUT\_, 2V/div TIMEBASE =  $1\mu$ s/div  $V_{DD}$  = +5V REF\_ = +4V ALL BITS ON TO ALL BITS OFF  $R_L$  =  $10k\Omega$ ,  $C_L$  = 100pF

### Pin Description

| Р      | IN     |                 |                                                                                                                                                                     |

|--------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX509 | MAX510 | NAME            | FUNCTION                                                                                                                                                            |

| 1      | 1      | OUTB            | DAC B Voltage Output                                                                                                                                                |

| 2      | 2      | OUTA            | DAC A Voltage Output                                                                                                                                                |

| 3      | 3      | Vss             | Negative Power Supply, 0V to -5V ±10%. Connect to AGND for single-supply operation.                                                                                 |

| 4      | -      | REFB            | Reference Voltage Input for DAC B                                                                                                                                   |

| _      | 4      | REFAB           | Reference Voltage Input for DACs A and B                                                                                                                            |

| 5      | _      | REFA            | Reference Voltage Input for DAC A                                                                                                                                   |

| 6      | 5      | AGND            | Analog Ground                                                                                                                                                       |

| 7, 14  | _      | N.C.            | Not Internally Connected                                                                                                                                            |

| 8      | 6      | DGND            | Digital Ground                                                                                                                                                      |

| 9      | 7      | LDAC            | Load DAC Input (active low). Driving this asynchronous input low (level sensitive) transfers the contents of each input latch to its respective DAC latch.          |

| 10     | 8      | DOUT            | Serial Data Output. Can sink and source current. Data at DOUT is adjustable to be clocked out on rising or falling edge of SCLK.                                    |

| 11     | 9      | CLR             | Clear DAC input (active low). Driving CLR low causes an asynchronous clear of input and DAC registers and sets all DAC outputs to zero.                             |

| 12     | 10     | DIN             | Serial Data Input. TTL/CMOS-compatible input. Data is clocked into DIN on the rising edge of SCLK. CS must be low for data to be clocked in.                        |

| 13     | 11     | SCLK            | Serial Clock Input. Data is clocked in on the rising edge and clocked out on either the rising (default) or the falling edge.                                       |

| 15     | 12     | CS              | Chip-Select Input (active low). Data is shifted in and out when $\overline{\text{CS}}$ is low. Programming commands are executed when $\overline{\text{CS}}$ rises. |

| 16     | _      | REFD            | Reference Voltage Input for DAC D                                                                                                                                   |

| _      | 13     | REFCD           | Reference Voltage Input for DACs C and D                                                                                                                            |

| 17     | -      | REFC            | Reference Voltage Input for DAC C                                                                                                                                   |

| 18     | 14     | V <sub>DD</sub> | Positive Power Supply, +5V ±10%                                                                                                                                     |

| 19     | 15     | OUTD            | DAC D Output Voltage                                                                                                                                                |

| 20     | 16     | OUTC            | DAC C Output Voltage                                                                                                                                                |

#### **Detailed Description**

#### Serial Interface

At power-on, the serial interface and all DACs are cleared and set to code zero. The serial data output (DOUT) is set to transition on SCLK's rising edge.

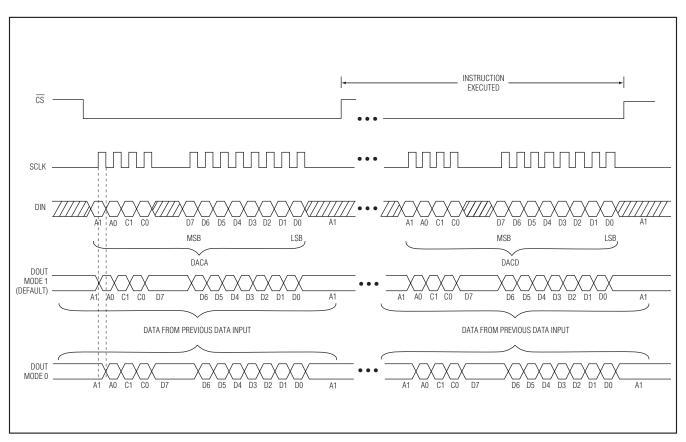

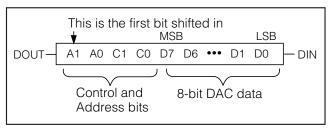

The MAX509/MAX510 communicate with microprocessors through a synchronous, full-duplex, 3-wire interface (Figure 1). Data is sent MSB first and can be transmitted in one 4-bit and one 8-bit (byte) packet or in one 12-bit word. If a 16-bit control word is used, the first four bits are ignored. A 4-wire interface adds a line for LDAC and allows asynchronous updating. The serial clock (SCLK) synchronizes the data transfer. Data is transmitted and received simultaneously.

Figure 2 shows a detailed serial interface timing. Please note that the clock should be low if it is stopped

between updates. DOUT does not go into a high-impedance state if the clock or  $\overline{\text{CS}}$  is high.

Serial data is clocked into the data registers in MSB-first format, with the address and configuration information preceding the actual DAC data. Data is clocked in on SCLK's rising edge while  $\overline{\text{CS}}$  is low. Data at DOUT is clocked out 12 clock cycles later, either at SCLK's rising edge (default or mode 1) or falling edge (mode 0).

Chip select (CS) must be low to enable the DAC. If CS is high, the interface is disabled and DOUT remains unchanged. CS must go low at least 40ns before the first rising edge of the clock pulse to properly clock in the first bit. With CS low, data is clocked into the MAX509/MAX510's internal shift register on the rising edge of the external serial clock. SCLK can be driven at rates up to 12.5MHz.

Figure 1. MAX509/MAX510 3-Wire Interface Timing

Figure 2. Detailed Serial Interface Timing (Mode 0 Shown)

#### **Table 1. Serial-Interface Programming Commands**

|    |    | 12-Bit Se | rial Word |                | LDAC | Function                                                                                                     |

|----|----|-----------|-----------|----------------|------|--------------------------------------------------------------------------------------------------------------|

| A1 | A0 | C1        | C0        | D7 D0          | LDAC | FullCtion                                                                                                    |

| 0  | 0  | 0         | 1         | 8-Bit DAC Data | 1    | Load DAC A input register, DAC output unchanged.                                                             |

| 0  | 1  | 0         | 1         | 8-Bit DAC Data | 1    | Load DAC B input register, DAC output unchanged.                                                             |

| 1  | 0  | 0         | 1         | 8-Bit DAC Data | 1    | Load DAC C input register, DAC output unchanged.                                                             |

| 1  | 1  | 0         | 1         | 8-Bit DAC Data | 1    | Load DAC D input register, DAC output unchanged.                                                             |

| 0  | 0  | 1         | 1         | 8-Bit DAC Data | 1    | Load input and DAC register A.                                                                               |

| 0  | 1  | 1         | 1         | 8-Bit DAC Data | 1    | Load input and DAC register B.                                                                               |

| 1  | 0  | 1         | 1         | 8-Bit DAC Data | 1    | Load input and DAC register C.                                                                               |

| 1  | 1  | 1         | 1         | 8-Bit DAC Data | 1    | Load input and DAC register D.                                                                               |

| X  | 0  | 0         | 0         | 8-Bit DAC Data | Х    | Update all DACs from shift register.                                                                         |

| Χ  | 1  | 0         | 0         | XXXXXXX        | Х    | No Operation (NOP), shifts data in shift register.                                                           |

| 0  | Х  | 1         | 0         | XXXXXXX        | Х    | "LDAC" Command, all DACs updated from respective input registers.                                            |

| 1  | 1  | 1         | 0         | xxxxxxx        | Х    | Mode 1, DOUT clocked out on rising edge of SCLK (default). All DACs updated from respective input registers. |

| 1  | 0  | 1         | 0         | xxxxxxx        | Х    | Mode 0, DOUT clocked out on falling edge of SCLK. All DACs updated from input registers.                     |

#### Serial Input Data Format and Control Codes

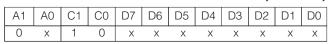

The 12-bit serial input format shown in Figure 3 comprises two DAC address bits (A1, A0), two control bits (C1, C0) and eight bits of data (D0...D7).

The 4-bit address/control code configures the DAC as shown in Table 1.

Figure 3. Serial Input Format

### Load Input Register, DAC Registers Unchanged (Single Update Operation)

| A1          | A0 | C1 | C0 | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|-------------|----|----|----|----|----|----|-------|------|----|----|----|

| Address 0 1 |    |    |    |    |    |    | 8-Bit | Data |    |    |    |

$(\overline{LDAC} = H)$

When performing a single update operation, A1 and A0 select the respective input register. At the rising edge of  $\overline{CS}$ , the selected input register is loaded with the current shift-register data. All DAC outputs remain unchanged. This preloads individual data in the input register without changing the DAC outputs.

#### Load Input and DAC Registers

| A1          | Α0 | C1 | C0 | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|-------------|----|----|----|----|----|----|-------|------|----|----|----|

| Address 1 1 |    |    |    |    |    |    | 8-Bit | Data |    |    |    |

$(\overline{\mathsf{LDAC}} = \mathsf{H})$

This command directly loads the selected DAC register at  $\overline{\text{CS}}$ 's rising edge. A1 and A0 set the DAC address. Current shift-register data is placed in the selected input and DAC registers.

For example, to load all four DAC registers simultaneously with individual settings (DAC A = 1V, DAC B = 2V, DAC C = 3V and DAC D = 4V), five commands are required. First, perform four single input register update operations. Next, perform an "LDAC" command as a fifth command. All DACs will be updated from their respective input registers at the rising edge of  $\overline{\text{CS}}$ .

#### Update All DACs from Shift Registers

| A1 | Α0 | C1 | C0 | D7             | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----------------|----|----|----|----|----|----|----|

| Х  | 0  | 0  | 0  | 8-Bit DAC Data |    |    |    |    |    |    |    |

$(\overline{LDAC} = x)$

All four DAC registers are updated with shift-register data. This command allows all DACs to be set to any analog value within the reference range. This command can be used to substitute  $\overline{\text{CLR}}$  if code 00 hex is programmed, which clears all DACs.

#### No Operation (NOP)

| Α1 | Α0 | C1 | C0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|----|----|----|----|

| Χ  | 1  | 0  | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

$(\overline{LDAC} = x)$

The NOP command (no operation) allows data to be shifted through the MAX509/MAX510 shift register without affecting the input or DAC registers. This is useful in daisy chaining (also see the *Daisy-Chaining Devices* section). For this command, the data bits are "Don't Cares." As an example, three MAX509/MAX510s are daisy-chained (A, B and C), and DAC A and DAC C need to be updated. The 36-bit-wide command would consist of one 12-bit word for device C, followed by an NOP instruction for device B and a third 12-bit word with data for device A. At  $\overline{CS}$ 's rising edge, only device B is not updated.

#### "LDAC" Command (Software)

$(\overline{LDAC} = x)$

All DAC registers are updated with the contents of their respective input registers at  $\overline{\text{CS}}$ 's rising edge. With the exception of using  $\overline{\text{CS}}$  to execute, this performs the same function as the asynchronous  $\overline{\text{LDAC}}$ .

#### Set DOUT Phase - SCLK Rising (Mode 1, Default)

| A1 | A0 | C1 | C0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|----|----|----|----|

| 1  | 1  | 1  | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

$(\overline{LDAC} = x)$

Mode 1 resets the serial output DOUT to transition at SCLK's rising edge. This is the MAX509/MAX510's default setting after the supply voltage has been applied.

The command also loads all DAC registers with the contents of their respective input registers, and is identical to the "LDAC" command.

#### Set DOUT Phase - SCLK Falling (Mode 0)

| Δ | ۱1 | Α0 | C1 | C0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|----|----|----|----|----|----|----|----|----|----|----|----|

|   | 1  | 0  | 1  | 0  | Х  | Х  | Х  | Х  | Х  | Χ  | Х  | Х  |

$(\overline{LDAC} = x)$

This command resets DOUT to transition at SCLK's falling edge. Once this command is issued, the phase of DOUT is latched and will not change except on power-up or if the specific command is issued that sets the phase to rising edge.

The same command also updates all DAC registers with the contents of their respective input registers, identical to the "LDAC" command.

#### **LDAC** Operation (Hardware)

LDAC is typically used in 4-wire interfaces (Figure 7). LDAC allows asynchronous hardware control of the DAC outputs and is level-sensitive. With LDAC low, the DAC registers are transparent and any time an input register is updated, the DAC output immediately follows.

#### Clear DACs with CLR

Strobing the  $\overline{\text{CLR}}$  pin low causes an asynchronous clear of input and DAC registers and sets all DAC outputs to zero. Similar to the  $\overline{\text{LDAC}}$  pin,  $\overline{\text{CLR}}$  can be invoked at any time, typically when the device is not selected ( $\overline{\text{CS}}$  = H). When the DAC data is all zeros, this function is equivalent to the "Update all DACs from Shift Registers" command.

#### Digital Inputs and Outputs

Digital inputs and outputs are compatible with both TTL and 5V CMOS logic. The power-supply current ( $I_{DD}$ ) depends on the input logic levels. Using CMOS logic to drive  $\overline{CS}$ , SCLK, DIN,  $\overline{CLR}$  and  $\overline{LDAC}$  turns off the internal level translators and minimizes supply currents.

#### Serial Data Output

DOUT is the output of the internal shift register. DOUT can be programmed to clock out data on SCLK's falling edge (mode 0) or rising edge (mode 1). In mode 0, output data lags the input data by 12.5 clock cycles, maintaining compatibility with Microwire, SPI, and QSPI. In mode 1, output data lags the input by 12 clock cycles. On power-up, DOUT defaults to mode 1 timing. DOUT never three-states; it always actively drives either high or low and remains unchanged when  $\overline{\text{CS}}$  is high.

#### Interfacing to the Microprocessor

The MAX509/MAX510 are Microwire, SPI, and QSPI compatible. For SPI and QSPI, clear the CPOL and CPHA configuration bits (CPOL = CPHA = 0). The SPI/QSPI CPOL = CPHA = 1 configuration can also be used if the DOUT output is ignored.

Figure 4. Connections for MICROWIRE

Figure 5. Connections for SPI

The MAX509/MAX510 can interface with Intel's 80C5X/80C3X family in mode 0 if the SCLK clock polarity is inverted. More universally, if a serial port is not available, three lines from one of the parallel ports can be used for bit manipulation.

Digital feedthrough at the voltage outputs is greatly minimized by operating the serial clock only to update the registers. Also see the Clock Feedthrough photo in the *Typical Operating Characteristics* section. The clock idle state is low.

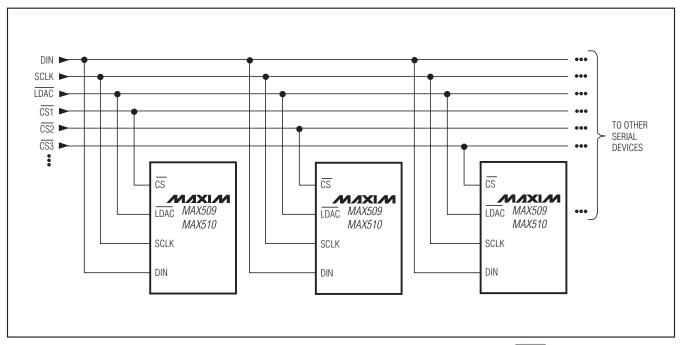

#### Daisy-Chaining Devices

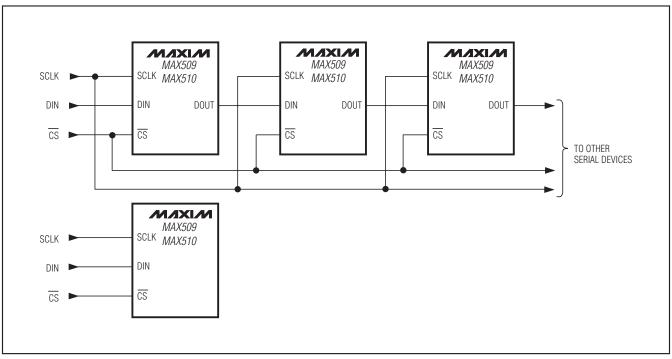

Any number of MAX509/MAX510s can be daisy-chained by connecting the DOUT pin of one device to the DIN pin of the following device in the chain. The NOP instruction (Table 1) allows data to be passed from DIN to DOUT without changing the input or DAC registers of the passing device. A three-wire interface updates daisy-chained or individual MAX509/MAX510s simultaneously by bringing  $\overline{\text{CS}}$  high.

Figure 6. Daisy-chained or individual MAX509/MAX510s are simultaneously updated by bringing  $\overline{CS}$  high. Only three wires are required.

Figure 7. Multiple MAX509/MAX510 DACs sharing one DIN line. Simultaneously update by strobing  $\overline{\text{LDAC}}$ , or specifically update by enabling individual  $\overline{\text{CS}}$ .

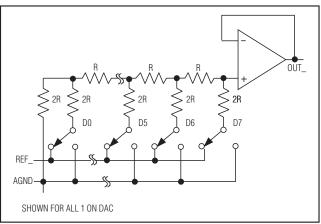

Figure 8. DAC Simplified Circuit Diagram

If multiple devices share a common DIN line, Figure 7's configuration provides simultaneous update by strobing LDAC low. CS1, CS2, CS3... are driven separately, thus controlling which data are written to devices 1, 2, 3....

### **Analog Section**DAC Operation

The MAX509/MAX510 contain four matched voltageoutput DACs. The DACs are inverted R-2R ladder networks that convert 8-bit digital words into equivalent analog output voltages in proportion to the applied reference voltages. Each DAC in the MAX509 has a separate reference input, while the two reference inputs in the MAX510 each share a pair of DACs. The two reference inputs permit different full-scale output voltage ranges for each pair of DACs. A simplified diagram of one of the four DACs is shown in Figure 8.

#### Reference Input

The MAX509/MAX510 can be used for multiplying applications. The reference accepts both DC and AC signals. The voltage at each REF input sets the fullscale output voltage for its respective DAC(s). If the reference voltage is positive, both the MAX509 and MAX510 can be operated from a single supply. If dual supplies are used, the reference input can vary from VSS to VDD, but is always referred to AGND. The input impedance at REF is code dependent, with the lowest value (16k $\Omega$  for the MAX509 and 8k $\Omega$  for the MAX510) occurring when the input code is 55 hex or 0101 0101. The maximum value, practically infinity, occurs when the input code is 00 hex. Since the REF input impedance is code dependent, the DAC's reference sources must have a low output impedance (no more than  $32\Omega$ for the MAX509 and  $16\Omega$  for the MAX510) to maintain output linearity. The REF input capacitance is also code

dependent: 15pF typical for the MAX509 and 30pF typical for the MAX510.

The output voltage for any DAC can be represented by a digitally programmable voltage source as:

$$VOUT = (NB \times VREF) / 256$$

where NB is the numerical value of the DAC's binary input code.

#### **Output Buffer Amplifiers**

All MAX509/MAX510 voltage outputs are internally buffered by precision unity-gain followers that slew at up to 1V/ $\mu$ s. The outputs can swing from VSS to VDD. With a 0V to +4V (or +4V to 0V) output transition, the amplifier outputs will settle to 1/2LSB in typically 6 $\mu$ s when loaded with 10k $\Omega$  in parallel with 100pF.

The buffer amplifiers are stable with any combination of resistive loads  $\geq 2k\Omega$  and capacitive loads  $\leq 300pF$ .

#### \_Applications Information

### Power Supply and Reference Operating Ranges

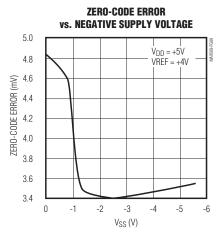

The MAX509/MAX510 are fully specified to operate with  $V_{DD} = 5V \pm 10\%$  and  $V_{SS} = 0V$  to -5.5V. 8-bit performance is guaranteed for both single- and dual-supply operation. The zero-code output error is less than 14mV when operating from a single +5V supply.

The DACs work well with reference voltages from  $V_{SS}$  to  $V_{DD}$ . The reference voltage is referred to AGND.

The preferred power-up sequence is to apply VSS and then VDD, but bringing up both supplies at the same time is also acceptable. In either case, the voltage applied to REF should not exceed VDD during power-up or at any other time. If proper power sequencing is not possible, connect an external Schottky diode between VSS and AGND to ensure compliance with the Absolute Maximum Ratings. Do not apply signals to the digital inputs before the device is fully powered up.

### Power-Supply Bypassing and Ground Management

In single-supply operation (AGND = DGND = Vss = 0V), AGND, DGND and Vss should be connected together in a "star" ground at the chip. This ground should then return to the highest quality ground available. Bypass  $V_{DD}$  with a  $0.1\mu F$  capacitor, located as close to  $V_{DD}$  and DGND as possible. In dual-supply operation, bypass Vss to AGND with  $0.1\mu F$ .

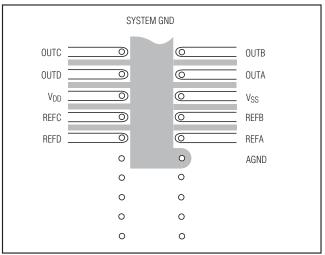

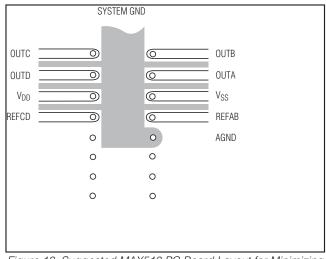

Careful PC board layout minimizes crosstalk among DAC outputs, reference inputs, and digital inputs. Figures 9 and 10 show suggested circuit board layouts to minimize crosstalk.

Figure 9. Suggested MAX509 PC Board Layout for Minimizing Crosstalk (Bottom View)

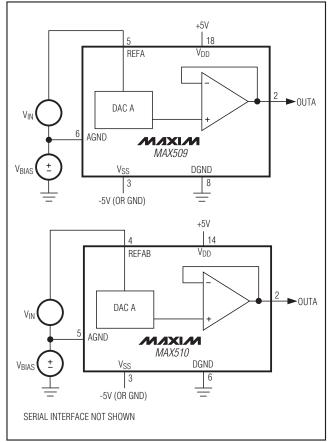

#### **Unipolar-Output, 2-Quadrant Multiplication**

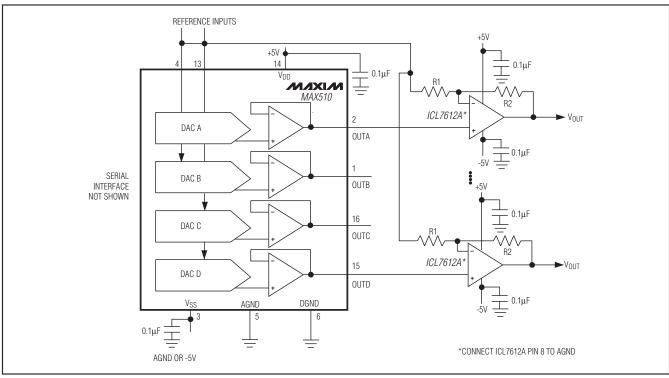

In unipolar operation, the output voltages and the reference input(s) are the same polarity. Figures 11 and 12 show the MAX509/MAX510 unipolar configurations. Both devices can be operated from a single supply if the reference inputs are positive. If dual supplies are used, the reference input can vary from VSS to VDD. Table 2 shows the unipolar code.

**Table 2. Unipolar Code Table**

| DAC CO | NTENTS | ANALOG                                                      |

|--------|--------|-------------------------------------------------------------|

| MSB    | LSB    | OUTPUT                                                      |

| 1111   | 1111   | $+V_{REF} \left(\frac{255}{256}\right)$                     |

| 1000   | 0001   | $+V_{REF} \left(\frac{129}{256}\right)$                     |

| 1000   | 0000   | $+V_{REF}\left(\frac{128}{256}\right) = +\frac{V_{REF}}{2}$ |

| 0111   | 1111   | $+V_{REF} \left(\frac{127}{256}\right)$                     |

| 0000   | 0001   | $+V_{REF}\left(\frac{1}{256}\right)$                        |

| 0000   | 0000   | OV                                                          |

**Note:** 1LSB =  $(V_{REF})(2^{-8}) = +V_{REF}(\frac{1}{256})$

Figure 10. Suggested MAX510 PC Board Layout for Minimizing Crosstalk (Bottom View)

#### Bipolar-Output, 2-Quadrant Multiplication

Bipolar-output, 2-quadrant multiplication is achieved by offsetting AGND positively or negatively. Table 3 shows the bipolar code.

AGND can be biased above DGND to provide an arbitrary nonzero output voltage for a 0 input code, as shown in Figure 13. The output voltage at OUTA is:

$$V_{OUTA} = V_{BIAS} + (NB/256)(V_{IN}),$$

**Table 3. Bipolar Code Table**

| DAC CO | NTENTS | ANALOG                                            |

|--------|--------|---------------------------------------------------|

| MSB    | LSB    | OUTPUT                                            |

| 1111   | 1111   | $+V_{REF} \left(\frac{127}{128}\right)$           |

| 1000   | 0001   | $+V_{REF}\left(\frac{1}{128}\right)$              |

| 1000   | 0000   | OV                                                |

| 0111   | 1111   | $-V_{REF}\left(\frac{1}{128}\right)$              |

| 0000   | 0001   | $-V_{REF} \left(\frac{127}{128}\right)$           |

| 0000   | 0000   | $-V_{REF}\left(\frac{128}{128}\right) = -V_{REF}$ |

Figure 11. MAX509 Unipolar Output Circuit

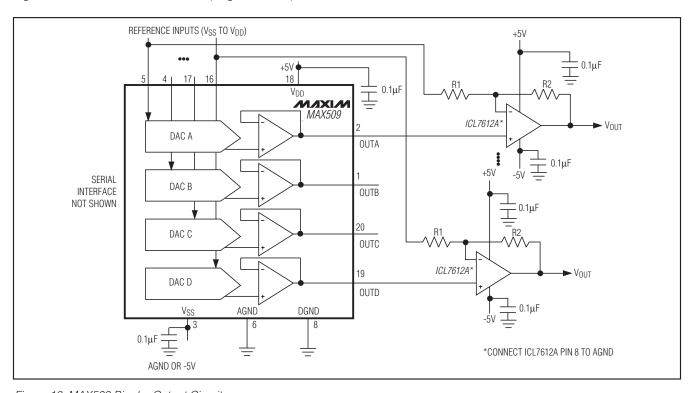

Figure 12. MAX510 Unipolar Output Circuit

Figure 13. MAX509/MAX510 AGND Bias Circuits (Positive Offset)

where NB represents the digital input word. Since AGND is common to all four DACs, all outputs will be offset by  $V_{BIAS}$  in the same manner. Do not bias AGND more than +1V above DGND, or more than 2.5V below DGND.

Figures 14 and 15 illustrate the generation of negative offsets with bipolar outputs. In these circuits, AGND is biased negatively (up to -2.5V with respect to DGND) to provide an arbitrary negative output voltage for a 0 input code. The output voltage at OUTA is:

OUTA = -(R2/R1)(2.5V) + (NB/256)(2.5V)(R2/R1+1)

where NB represents the digital input word. Since AGND is common to all four DACs, all outputs will be offset by  $V_{BIAS}$  in the same manner. Table 3, with  $V_{REF} = 2.5V$ , shows the digital code vs. output voltage for Figure 14 and 15's circuits with R1 = R2. The ICL7612 op amp is chosen because its common-mode range extends to both supply rails.

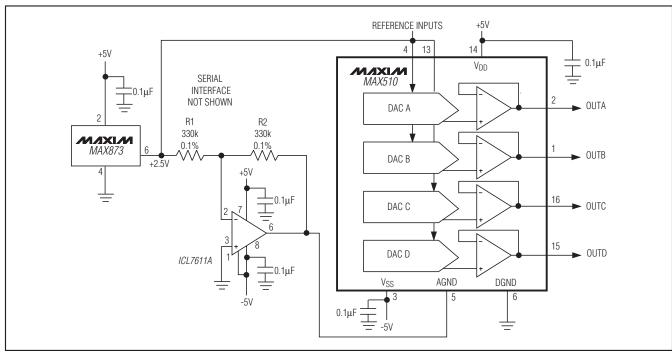

Figure 14. MAX509 AGND Bias Circuit (Negative Offset)

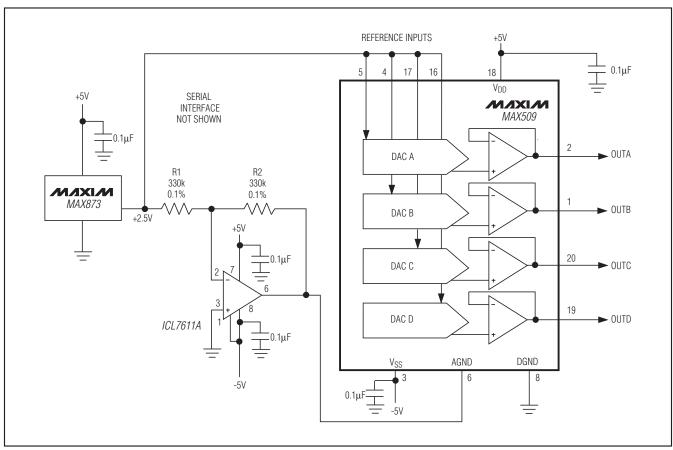

#### **4-Quadrant Multiplication**

Each DAC output may be configured for 4-quadrant multiplication using Figure 16 and 17's circuit. One op amp and two resistors are required per channel. With R1 = R2:

$$V_{OUT} = V_{REF} [2(NB/256)-1]$$

where NB represents the digital word in DAC register A. The recommended value for resistors R1 and R2 is  $330k\Omega$  (±0.1%). Table 3 shows the digital code vs. output voltage for Figure 16 and 17's circuit.

Figure 15. MAX510 AGND Bias Circuit (Negative Offset)

Figure 16. MAX509 Bipolar Output Circuit

Figure 17. MAX510 Bipolar Output Circuit

#### Functional Diagrams (continued)

#### \_Pin Configurations (continued)

#### \_Ordering Information (continued)

| PART        | TEMP RANGE      | PIN-PACKAGE | TUE<br>(LSB) |

|-------------|-----------------|-------------|--------------|

| MAX509BCAP+ | 0°C to +70°C    | 20 SSOP     | ±1.5         |

| MAX509AEPP+ | -40°C to +85°C  | 20 PDIP     | ±1           |

| MAX509BEPP+ | -40°C to +85°C  | 20 PDIP     | ±1.5         |

| MAX509AEWP+ | -40°C to +85°C  | 20 Wide SO  | ±1           |

| MAX509BEWP+ | -40°C to +85°C  | 20 Wide SO  | ±1.5         |

| MAX509AEAP+ | -40°C to +85°C  | 20 SSOP     | ±1           |

| MAX509BEAP+ | -40°C to +85°C  | 20 SSOP     | ±1.5         |

| MAX509AMJP  | -55°C to +125°C | 20 CERDIP** | ±1           |

| MAX509BMJP  | -55°C to +125°C | 20 CERDIP** | ±1.5         |

| MAX510ACPE+ | 0°C to +70°C    | 16 PDIP     | ±1           |

| MAX510BCPE+ | 0°C to +70°C    | 16 PDIP     | ±1.5         |

| MAX510ACWE+ | 0°C to +70°C    | 16 Wide SO  | ±1           |

| MAX510BCWE+ | 0°C to +70°C    | 16 Wide SO  | ±1.5         |

| MAX510AEPE+ | -40°C to +85°C  | 16 PDIP     | ±1           |

| MAX510BEPE+ | -40°C to +85°C  | 16 PDIP     | ±1.5         |

| MAX510AEWE+ | -40°C to +85°C  | 16 Wide SO  | ±1           |

| MAX510BEWE+ | -40°C to +85°C  | 16 Wide SO  | ±1.5         |

| MAX510AMJE  | -55°C to +125°C | 16 CERDIP** | ±1           |

| MAX510BMJE  | -55°C to +125°C | 16 CERDIP** | ±1.5         |

<sup>\*\*</sup>Contact factory for availability and processing to MIL-STD-883.

#### Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 20 PDIP         | P20+3           | 21-0043        | _                   |

| 20 Wide SO      | W20+3           | 21-0042        | 90-0108             |

| 20 SSOP         | A20A+1          | 21-0056        | 90-0094             |

| 20 CERDIP       | J20-2           | 21-0045        | _                   |

| 16 PDIP         | P16+2           | 21-0043        | _                   |

| 16 Wide SO      | W16+3           | 21-0042        | 90-0107             |

| 16 CERDIP       | J16-3           | 21-0045        | _                   |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Revision History**

| REVISION | REVISION | DESCRIPTION                                                                                                                             | PAGES        |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| NUMBER   | DATE     |                                                                                                                                         | CHANGED      |

| 3        | 12/10    | Updated Ordering Information, added soldering temperature to <i>Absolute</i> Maximum Ratings, updated Figure 17 and Functional Diagrams | 1, 2, 19, 20 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_Ordering Information (continued)

| PART        | TEMP RANGE      | PIN-PACKAGE | TUE<br>(LSB) |

|-------------|-----------------|-------------|--------------|

| MAX509BCAP+ | 0°C to +70°C    | 20 SSOP     | ±1.5         |

| MAX509AEPP+ | -40°C to +85°C  | 20 PDIP     | ±1           |

| MAX509BEPP+ | -40°C to +85°C  | 20 PDIP     | ±1.5         |

| MAX509AEWP+ | -40°C to +85°C  | 20 Wide SO  | ±1           |

| MAX509BEWP+ | -40°C to +85°C  | 20 Wide SO  | ±1.5         |

| MAX509AEAP+ | -40°C to +85°C  | 20 SSOP     | ±1           |

| MAX509BEAP+ | -40°C to +85°C  | 20 SSOP     | ±1.5         |

| MAX509AMJP  | -55°C to +125°C | 20 CERDIP** | ±1           |

| MAX509BMJP  | -55°C to +125°C | 20 CERDIP** | ±1.5         |

| MAX510ACPE+ | 0°C to +70°C    | 16 PDIP     | ±1           |

| MAX510BCPE+ | 0°C to +70°C    | 16 PDIP     | ±1.5         |

| MAX510ACWE+ | 0°C to +70°C    | 16 Wide SO  | ±1           |

| MAX510BCWE+ | 0°C to +70°C    | 16 Wide SO  | ±1.5         |

| MAX510AEPE+ | -40°C to +85°C  | 16 PDIP     | ±1           |

| MAX510BEPE+ | -40°C to +85°C  | 16 PDIP     | ±1.5         |

| MAX510AEWE+ | -40°C to +85°C  | 16 Wide SO  | ±1           |

| MAX510BEWE+ | -40°C to +85°C  | 16 Wide SO  | ±1.5         |

| MAX510AMJE  | -55°C to +125°C | 16 CERDIP** | ±1           |

| MAX510BMJE  | -55°C to +125°C | 16 CERDIP** | ±1.5         |

<sup>\*\*</sup>Contact factory for availability and processing to MIL-STD-883.

#### Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 20 PDIP         | P20+3           | 21-0043        | _                   |

| 20 Wide SO      | W20+3           | 21-0042        | 90-0108             |

| 20 SSOP         | A20A+1          | 21-0056        | 90-0094             |

| 20 CERDIP       | J20-2           | 21-0045        | _                   |

| 16 PDIP         | P16+2           | 21-0043        | _                   |

| 16 Wide SO      | W16+3           | 21-0042        | 90-0107             |

| 16 CERDIP       | J16-3           | 21-0045        | _                   |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### **Analog Devices Inc.:**

MAX509ACAP+T MAX509BCPP+ MAX509BCWP+ MAX509ACAP+ MAX509ACAP+ MAX509AEAP+T MAX509AEAP+T MAX509AEWP+ MAX509BCWP+T MAX509BEAP+ MAX509BEAP+T