## LMP2021/LMP2022 Zero Drift, Low Noise, EMI Hardened Amplifiers **General Description**

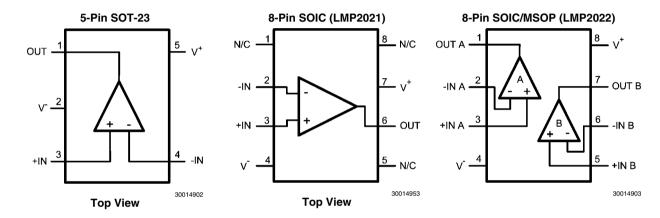

The LMP2021/LMP2022 are single and dual precision operational amplifiers offering ultra low input offset voltage, near zero input offset voltage drift, very low input voltage noise and very high open loop gain. They are part of the LMP® precision family and are ideal for instrumentation and sensor interfaces. The LMP2021/LMP2022 have only 0.004 µV/°C of input offset voltage drift, and 0.4 µV of input offset voltage. These attributes provide great precision in high accuracy applications. The proprietary continuous correction circuitry guarantees impressive CMRR and PSRR, removes the 1/f noise component, and eliminates the need for calibration in many circuits. With only 260  $nV_{PP}$  (0.1 Hz to 10 Hz) of input voltage noise and no 1/f noise component, the LMP2021/LMP2022 are suitable for low frequency applications such as industrial precision weigh scales. The low input bias current of 23 pA makes these excellent choices for high source impedance circuits such as non-invasive medical instrumentation as well as test and measurement equipment. The extremely high open loop gain of 160 dB drastically reduces gain error in high gain applications. With ultra precision DC specifications and very low noise, the LMP2021/LMP2022 are ideal for position sensors, bridge sensors, pressure sensors, medical equipment and other high accuracy applications with very low error budgets. The LMP2021 is offered in 5-Pin SOT-23 and 8-Pin SOIC packages. The LMP2022 is offered in 8-Pin MSOP and 8-Pin SOIC packages.

### **Features**

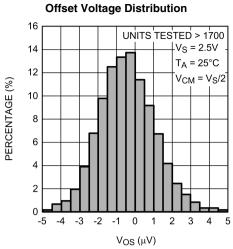

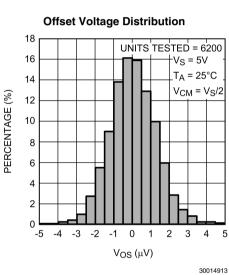

(Typical Values,  $T_A = 25^{\circ}C$ ,  $V_S = 5V$ )

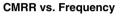

Input offset voltage (typical) –0.4 µV Input offset voltage (max) . ±5 μV Input offset voltage drift (typical) -0.004 uV/°C -Input offset voltage drift (max) ±0.02 µV/°C 11 nV/√Hz Input voltage noise,  $A_{y} = 1000$ 160 dB Open loop gain 139 dB CMRR PSRR 130 dB 2.2V to 5.5V Supply voltage range Supply current (per amplifier) 1.1 mA Input bias current ±25 pA -GBW 5 MHz Slew rate 2.6 V/us Operating temperature range -40°C to 125°C 5-Pin SOT-23, 8-Pin MSOP and 8-Pin SOIC Packages

### Applications

- Precision instrumentation amplifiers

- Battery powered instrumentation

- Thermocouple amplifiers

- Bridge amplifiers

LMP® is a registered trademark of National Semiconductor Corporation.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)                    |                 |

|-------------------------------------------|-----------------|

| Human Body Model                          | 2000V           |

| Machine Model                             | 200V            |

| Charge Device Model                       | 1000V           |

| V <sub>IN</sub> Differential              | ±V <sub>S</sub> |

| Supply Voltage ( $V_S = V^+ - V^-$ )      | 6.0V            |

| Output Short-Circuit Duration to V+ or V- |                 |

| (Note 3)                                  | 5s              |

| Storage Temperature Range                 | –65°C to 150°C  |

| Junction Temperature (Note 4)             | 150°C max       |

### 2.5V Electrical Characteristics (Note 5)

#### Soldering Information Infrared or Convection (20 sec) 235°C Wave Soldering Lead Temperature (10 sec) 260°C

### Operating Ratings (Note 1)

| Temperature Range                            | –40°C to 125°C |

|----------------------------------------------|----------------|

| Supply Voltage ( $V_S = V^+ - V^-$ )         | 2.2V to 5.5V   |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                |

| 5-Pin SOT-23                                 | 164 °C/W       |

| 8-Pin SOIC (LMP2021)                         | 106 °C/W       |

| 8-Pin SOIC (LMP2022)                         | 106 °C/W       |

| 8-Pin MSOP                                   | 217 °C/W       |

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 2.5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $R_L > 10 \text{ k}\Omega$  to  $V^+/2$ . Bold-face limits apply at the temperature extremes.

| Symbol                                              | Parameter                                        |            | Conditions                                                                                   | Min<br>(Note 7)   | Typ<br>(Note 6) | Max<br>(Note 7)     | Units |  |

|-----------------------------------------------------|--------------------------------------------------|------------|----------------------------------------------------------------------------------------------|-------------------|-----------------|---------------------|-------|--|

| V <sub>OS</sub>                                     | Input Offset Voltage                             |            |                                                                                              |                   | -0.9            | ±5<br><b>±10</b>    | μV    |  |

| TCV <sub>OS</sub>                                   | Input Offset Voltage Drift (Note 8)              |            |                                                                                              |                   | 0.001           | ±0.02               | µV/°C |  |

| I <sub>B</sub>                                      | Input Bias Current                               |            |                                                                                              |                   | ±23             | ±100<br><b>±300</b> | pА    |  |

| I <sub>OS</sub>                                     | Input Offset Current                             |            |                                                                                              |                   | ±57             | ±200<br><b>±250</b> | pА    |  |

| CMRR                                                | Common Mode Rejection Ratio                      |            | $V \le V_{CM} \le 1.7V$<br>$V_{CM} \le 1.5V$                                                 | 105<br><b>102</b> | 141             |                     | dB    |  |

| CMVR                                                | Input Common-Mode Voltage Range                  |            | e Signal CMRR ≥ 105 dB<br>e Signal CMRR ≥ 102 dB                                             | -0.2<br>0         |                 | 1.7<br><b>1.5</b>   | V     |  |

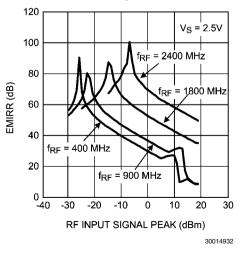

| EMIRR Electro-Magnetic Interfere<br>Rejection Ratio | Electro-Magnetic Interference<br>Rejection Ratio |            | $V_{\text{RF-PEAK}} = 100 \text{ mV}_{\text{P}} (-20 \text{ dBV}_{\text{P}})$<br>f = 400 MHz |                   | 40              |                     |       |  |

|                                                     | (Note 9)                                         | IN+<br>and | V <sub>RF-PEAK</sub> = 100 mV <sub>P</sub> (–20 dBV <sub>P</sub> )<br>f = 900 MHz            |                   | 48              |                     | dB    |  |

|                                                     |                                                  | IN–        | V <sub>RF-PEAK</sub> = 100 mV <sub>P</sub> (–20 dBV <sub>P</sub> )<br>f = 1800 MHz           |                   | 67              |                     | uВ    |  |

|                                                     |                                                  |            | V <sub>RF-PEAK</sub> = 100 mV <sub>P</sub> (–20 dBV <sub>P</sub> )<br>f = 2400 MHz           |                   | 79              |                     |       |  |

| PSRR                                                | Power Supply Rejection Ratio                     | 2.5V       | $\leq$ V <sup>+</sup> $\leq$ 5.5V, V <sub>CM</sub> = 0                                       | 115<br><b>112</b> | 130             |                     | dB    |  |

|                                                     |                                                  | 2.2V       | $\leq V_{+} \leq 5.5V, V_{CM} = 0$                                                           | 110               | 130             |                     |       |  |

| A <sub>VOL</sub>                                    |                                                  |            | 124<br><b>119</b>                                                                            | 150               |                 | dB                  |       |  |

|                                                     |                                                  |            | 2 kΩ to V+/2<br>= 0.5V to 2V                                                                 | 120<br><b>115</b> | 150             |                     |       |  |

| Symbol           | Parameter                    | Conditions                                                                                                               | Min      | Тур                      | Max              | Units               |  |

|------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|------------------|---------------------|--|

|                  |                              |                                                                                                                          | (Note 7) | (Note 6)                 | (Note 7)         |                     |  |

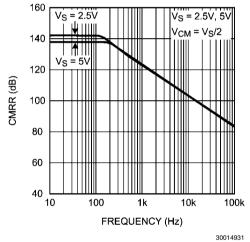

| V <sub>OUT</sub> | Output Swing High            | $R_L = 10 \text{ k}\Omega$ to V+/2                                                                                       |          | 38                       | 50               |                     |  |

|                  |                              |                                                                                                                          |          |                          | 70               | -                   |  |

|                  |                              | $R_L = 2 k\Omega$ to V+/2                                                                                                |          | 62                       | 85<br><b>115</b> | mV                  |  |

|                  | Output Swing Low             | $R_L = 10 \text{ k}\Omega \text{ to V+/2}$                                                                               |          | 30                       | 45<br><b>55</b>  | from either<br>rail |  |

|                  |                              | $R_L = 2 k\Omega$ to V+/2                                                                                                |          | 58                       | 75<br><b>95</b>  |                     |  |

| I <sub>OUT</sub> | Linear Output Current        | Sourcing, V <sub>OUT</sub> = 2V                                                                                          | 30       | 50                       |                  |                     |  |

|                  |                              | Sinking, $V_{OUT} = 0.5V$                                                                                                | 30       | 50                       |                  | - mA                |  |

| I <sub>s</sub>   | Supply Current               | Per Amplifier                                                                                                            |          | 0.95 1.10<br><b>1.37</b> |                  | mA                  |  |

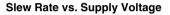

| SR               | Slew Rate (Note 10)          | $A_V = +1, C_L = 20 \text{ pF}, R_L = 10 \text{ k}\Omega$ 2.5<br>V <sub>O</sub> = 2 V <sub>PP</sub>                      |          |                          | V/µs             |                     |  |

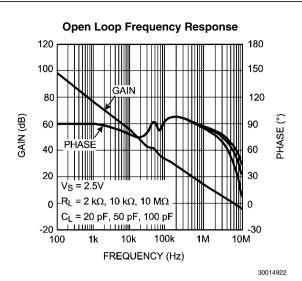

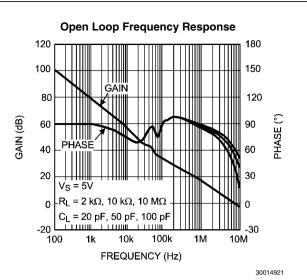

| GBW              | Gain Bandwidth Product       | $C_{L} = 20 \text{ pF}, R_{L} = 10 \text{ k}\Omega$                                                                      |          | 5                        |                  | MHz                 |  |

| G <sub>M</sub>   | Gain Margin                  | $C_L = 20 \text{ pF}, \text{ R}_L = 10 \text{ k}\Omega$                                                                  |          | 10                       |                  | dB                  |  |

| Φ <sub>M</sub>   | Phase Margin                 | $C_{L} = 20 \text{ pF}, R_{L} = 10 \text{ k}\Omega$                                                                      |          | 60                       |                  | deg                 |  |

| C <sub>IN</sub>  | Input Capacitance            | Common Mode                                                                                                              |          | 12                       |                  |                     |  |

|                  |                              | Differential Mode                                                                                                        |          | 12                       |                  | рF                  |  |

| e <sub>n</sub>   | Input-Referred Voltage Noise | f = 0.1 kHz or 10 kHz, A <sub>V</sub> = 1000                                                                             |          | 11                       |                  | nV/√Hz              |  |

|                  | Density                      | $f = 0.1 \text{ kHz} \text{ or } 10 \text{ kHz}, A_V = 100$                                                              |          | 15                       |                  | nv/√Hz              |  |

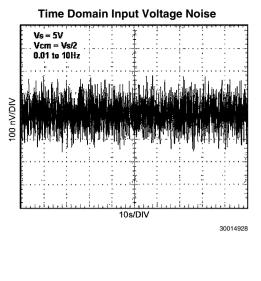

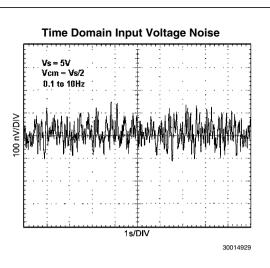

|                  | Input-Referred Voltage Noise | 0.1 Hz to 10 Hz                                                                                                          |          | 260                      |                  | nV <sub>PP</sub>    |  |

|                  |                              | 0.01 Hz to 10 Hz                                                                                                         |          | 330                      |                  | - nv <sub>PP</sub>  |  |

| i <sub>n</sub>   | Input-Referred Current Noise | f = 1 kHz                                                                                                                |          | 350                      |                  | fA/√Hz              |  |

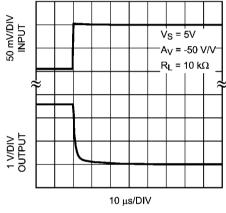

| t <sub>r</sub>   | Recovery time                | to 0.1%, R <sub>L</sub> = 10 kΩ, A <sub>V</sub> = -50,<br>V <sub>OUT</sub> = 1.25 V <sub>PP</sub> Step, Duration = 50 μs |          | 50                       |                  | μs                  |  |

| ст               | Cross Talk                   | LMP2022, f = 1 kHz                                                                                                       |          | 150                      |                  | dB                  |  |

### 5V Electrical Characteristics (Note 5)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $R_L > 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                           | Conditions                                               | Min<br>(Note 7)   | Typ<br>(Note 6) | Max<br>(Note 7)     | Units |

|-------------------|-------------------------------------|----------------------------------------------------------|-------------------|-----------------|---------------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage                |                                                          |                   | -0.4            | ±5<br>±10           | μV    |

| TCV <sub>OS</sub> | Input Offset Voltage Drift (Note 8) |                                                          |                   | -0.004          | ±0.02               | μV/°C |

| I <sub>B</sub>    | Input Bias Current                  |                                                          |                   | ±25             | ±100<br><b>±300</b> | pА    |

| I <sub>os</sub>   | Input Offset Current                |                                                          |                   | ±48             | ±200<br><b>±250</b> | pА    |

| CMRR              | Common Mode Rejection Ratio         | $-0.2V \le V_{CM} \le 4.2V$ $0V \le V_{CM} \le 4.0V$     | 120<br><b>115</b> | 139             |                     | dB    |

| CMVR              | Input Common-Mode Voltage Range     | Large Signal CMRR ≥ 120 dB<br>Large Signal CMRR ≥ 115 dB | -0.2<br>0         |                 | 4.2<br><b>4.0</b>   | V     |

www.national.com

3

| <b>N</b> |

|----------|

|          |

| ~        |

| 0        |

| N        |

| à        |

| <u>ш</u> |

|          |

| >        |

| _        |

|          |

| _        |

|          |

| _        |

| N        |

| 0        |

| Ñ        |

| Ô.       |

|          |

| 5        |

| <        |

|          |

|          |

|          |

| Symbol           | Parameter                                                     | Conditions                                                                                                           | Min               | Тур      | Max<br>(Note 7)     | Units              |  |

|------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------|----------|---------------------|--------------------|--|

|                  |                                                               |                                                                                                                      | (Note 7)          | (Note 6) |                     |                    |  |

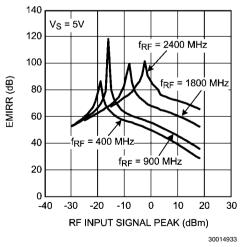

| EMIRR            | Electro-Magnetic Interference<br>Rejection Ratio              | V <sub>RF-PEAK</sub> = 100 mV <sub>P</sub> (–20 dBV <sub>P</sub> )<br>f = 400 MHz                                    |                   | 58       |                     |                    |  |

|                  | (Note 9)                                                      | IN+ $V_{\text{RF-PEAK}} = 100 \text{ mV}_{\text{P}} (-20 \text{ dBV}_{\text{P}})$<br>f = 900 MHz                     |                   | 64       |                     |                    |  |

|                  |                                                               | and $V_{RF-PEAK} = 100 \text{ mV}_{P} (-20 \text{ dBV}_{P})$<br>f = 1800 MHz                                         |                   | 72       |                     | dB                 |  |

|                  |                                                               | $V_{RF-PEAK} = 100 \text{ mV}_{P} (-20 \text{ dBV}_{P})$<br>f = 2400 MHz                                             |                   | 82       |                     |                    |  |

| PSRR             | Power Supply Rejection Ratio                                  | $2.5V \le V^+ \le 5.5V, V_{CM} = 0$                                                                                  | 115<br><b>112</b> | 130      |                     | dB                 |  |

|                  |                                                               | $2.2V \le V^+ \le 5.5V, V_{CM} = 0$                                                                                  | 110               | 130      |                     |                    |  |

| A <sub>VOL</sub> | Large Signal Voltage Gain                                     | $R_L = 10 k\Omega$ to V+/2<br>V <sub>OUT</sub> = 0.5V to 4.5V                                                        | 125<br><b>120</b> | 160      |                     |                    |  |

|                  |                                                               | $R_L = 2 \text{ k}\Omega \text{ to V}^+/2$<br>$V_{OUT} = 0.5V \text{ to } 4.5V$                                      | 123<br><b>118</b> | 160      |                     | dB                 |  |

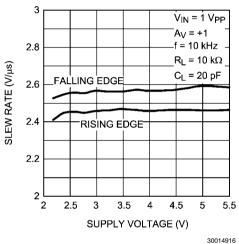

|                  | Output Swing High $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$ |                                                                                                                      |                   | 83       | 135<br><b>170</b>   |                    |  |

|                  |                                                               | $R_L = 2 \text{ k}\Omega \text{ to } V^+/2$                                                                          |                   | 120      | 160<br><b>204</b>   | mV                 |  |

|                  | Output Swing Low                                              | $R_L = 10 \text{ k}\Omega$ to V+/2                                                                                   |                   | 65       | 80<br><b>105</b>    | from<br>either rai |  |

|                  |                                                               | $R_L = 2 k\Omega$ to V+/2                                                                                            |                   | 103      | 125<br><b>158</b>   |                    |  |

| I <sub>OUT</sub> | Linear Output Current                                         | Sourcing, V <sub>OUT</sub> = 4.5V                                                                                    | 30                | 50       |                     | mA                 |  |

|                  |                                                               | Sinking, V <sub>OUT</sub> = 0.5V                                                                                     | 30                | 50       |                     |                    |  |

| I <sub>S</sub>   | Supply Current                                                | Per Amplifier                                                                                                        |                   | 1.1      | 1.25<br><b>1.57</b> | mA                 |  |

| SR               | Slew Rate (Note 10)                                           | $A_V = +1, C_L = 20 \text{ pF}, R_L = 10 \text{ k}\Omega$<br>$V_O = 2 \text{ V}_{PP}$                                |                   | 2.6      |                     | V/µs               |  |

| GBW              | Gain Bandwidth Product                                        | $C_{L} = 20 \text{ pF}, R_{L} = 10 \text{ k}\Omega$                                                                  |                   | 5        |                     | MHz                |  |

| G <sub>M</sub>   | Gain Margin                                                   | $C_{L} = 20 \text{ pF}, R_{L} = 10 \text{ k}\Omega$                                                                  |                   | 10       |                     | dB                 |  |

| Φ <sub>M</sub>   | Phase Margin                                                  | $C_{L} = 20 \text{ pF}, R_{L} = 10 \text{ k}\Omega$                                                                  |                   | 60       |                     | deg                |  |

| C <sub>IN</sub>  | Input Capacitance                                             | Common Mode                                                                                                          |                   | 12       |                     |                    |  |

|                  |                                                               | Differential Mode                                                                                                    |                   | 12       |                     | pF                 |  |

| e <sub>n</sub>   | Input-Referred Voltage Noise Density                          | f = 0.1 kHz or 10 kHz, A <sub>V</sub> = 1000                                                                         |                   | 11       |                     | nV/√Hz             |  |

|                  |                                                               | f = 0.1 kHz or 10 kHz, A <sub>V</sub> = 100                                                                          |                   | 15       |                     | HV/√HZ             |  |

|                  | Input-Referred Voltage Noise                                  | 0.1 Hz to 10 Hz Noise                                                                                                |                   | 260      |                     | nV <sub>PP</sub>   |  |

|                  |                                                               | 0.01 Hz to 10 Hz Noise                                                                                               |                   | 330      |                     |                    |  |

| i <sub>n</sub>   | Input-Referred Current Noise                                  | f = 1 kHz                                                                                                            |                   | 350      |                     | fA/√Hz             |  |

| t <sub>r</sub>   | Input Overload Recovery time                                  | to 0.1%, $R_L = 10 \text{ k}\Omega$ , $A_V = -50$ ,<br>V <sub>OUT</sub> = 2.5 V <sub>PP</sub> Step, Duration = 50 μs |                   | 50       |                     | μs                 |  |

| СТ               | Cross Talk                                                    | LMP2022, f = 1 kHz                                                                                                   |                   | 150      |                     | dB                 |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics Tables.

Note 2: Human Body Model per MIL-STD-883, Method 3015.7. Machine Model, per JESD22-A115-A. Field-Induced Charge-Device Model, per JESD22-C101-C.

Note 3: Package power dissipation should be observed.

**Note 4:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

**Note 5:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

Note 6: Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 7: All limits are guaranteed by testing, statistical analysis or design.

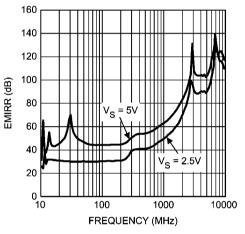

**Note 8:** Offset voltage temperature drift is determined by dividing the change in  $V_{OS}$  at the temperature extremes by the total temperature change. **Note 9:** The EMI Rejection Ratio is defined as EMIRR = 20Log ( $V_{R_{P,PEAK}}/\Delta V_{OS}$ ).

Note 10: The number specified is the average of rising and falling slew rates and is measured at 90% to 10%.

### **Connection Diagrams**

### **Ordering Information**

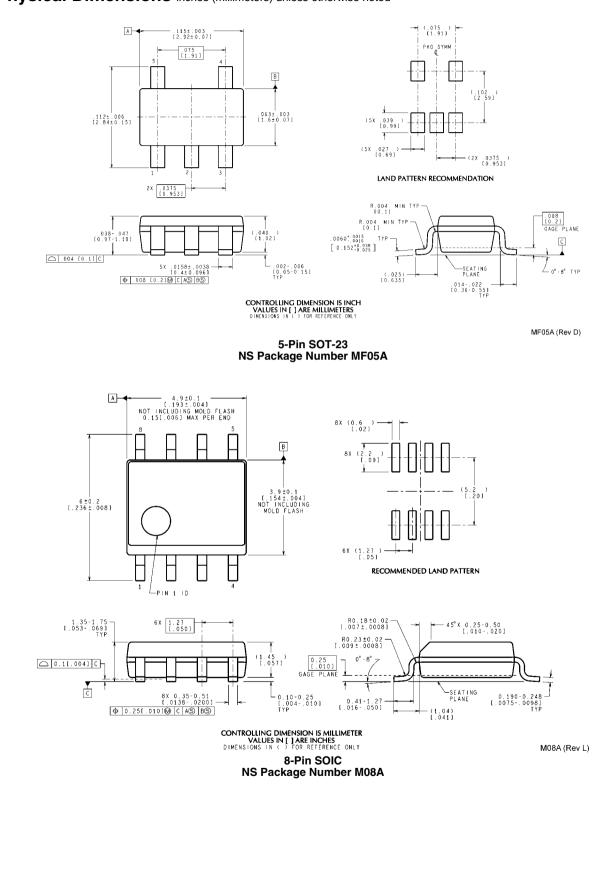

| Package      | Part Number | Package Marking Transport Media |                          | NSC Drawing |

|--------------|-------------|---------------------------------|--------------------------|-------------|

|              | LMP2021MF   |                                 | 1k Units Tape and Reel   |             |

| 5-Pin SOT-23 | LMP2021MFE  | AF5A                            | 250 Units Tape and Reel  | MF05A       |

|              | LMP2021MFX  |                                 | 3k Units Tape and Reel   |             |

|              | LMP2021MA   | LMP2021MA                       | 95 Units/Rail            |             |

| 8-Pin SOIC   | LMP2021MAX  | LIVIP2021IVIA                   | 2.5k Units Tape and Reel | M08A        |

| 0-PIII 3010  | LMP2022MA   | LMP2022MA                       | 95 Units/Rail            | WUOA        |

|              | LMP2022MAX  | LIVIPZUZZIVIA                   | 2.5k Units Tape and Reel |             |

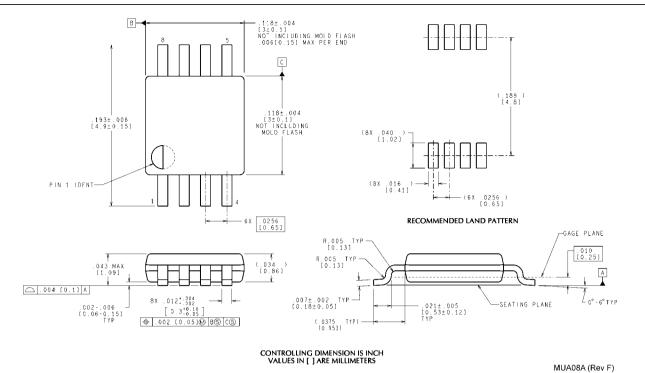

|              | LMP2022MM   |                                 | 1k Units Tape and Reel   |             |

| 8-Pin MSOP   | LMP2022MME  | LMP2022MME AV5A                 |                          | MUA08A      |

|              | LMP2022MMX  |                                 | 3.5k Units Tape and Reel |             |

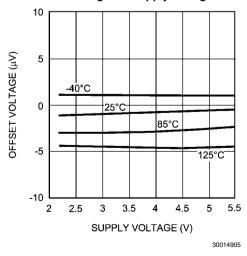

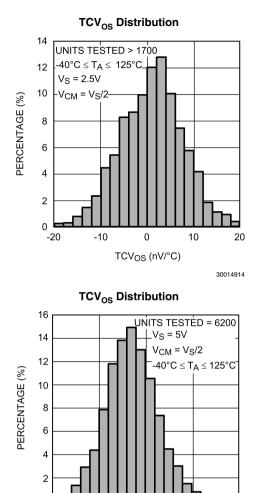

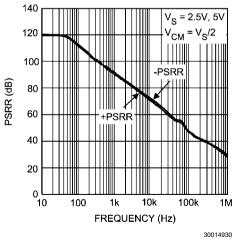

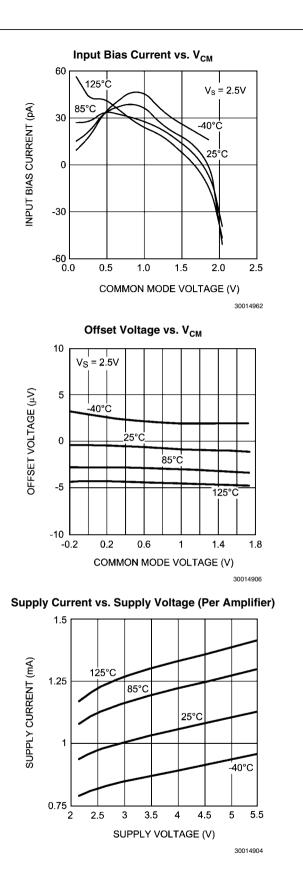

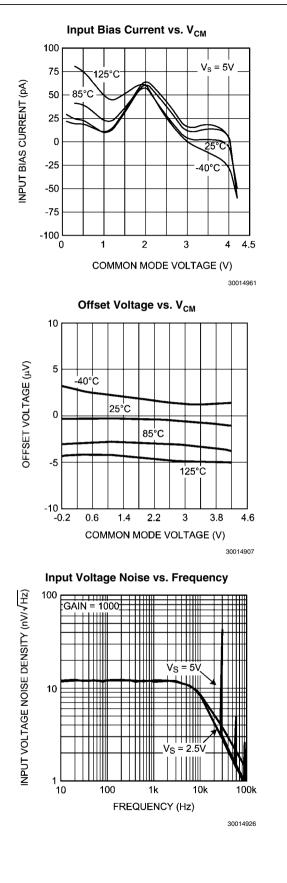

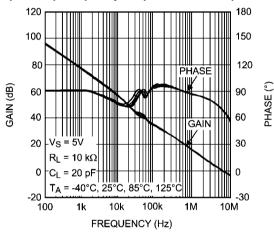

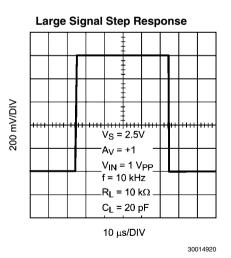

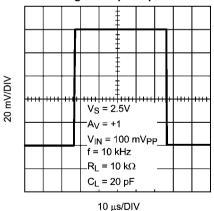

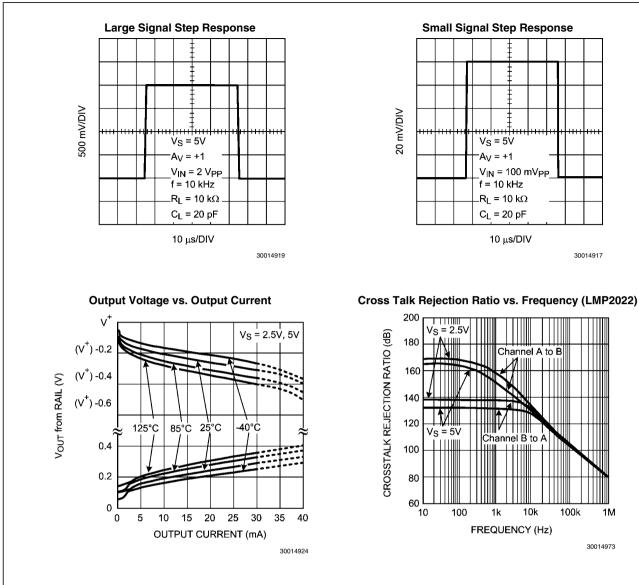

# **Typical Performance Characteristics** Unless otherwise noted: $T_A = 25^{\circ}C$ , $R_L > 10 \text{ k}\Omega$ , $V_S = V^+ - V^-$ , $V_S = 5V$ , $V_{CM} = V_S/2$ .

30014912

Offset Voltage vs. Supply Voltage

30014915

20

10

PSRR vs. Frequency

0

TCV<sub>OS</sub> (nV/°C)

-10

0

-20

**Open Loop Frequency Response Over Temperature**

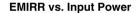

**EMIRR vs. Frequency**

30014934

EMIRR vs. Input Power

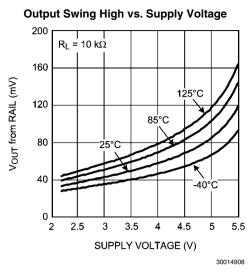

Output Swing High vs. Supply Voltage

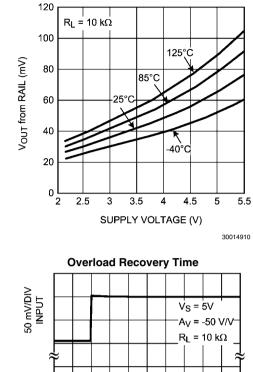

**Output Swing Low vs. Supply Voltage**

**Output Swing Low vs. Supply Voltage**

30014943

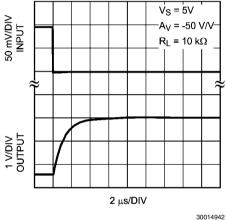

#### **Small Signal Step Response**

30014918

1M

30014973

### **Application Information**

#### LMP2021/LMP2022

The LMP2021/LMP2022 are single and dual precision operational amplifiers with ultra low offset voltage, ultra low offset voltage drift, and very low input voltage noise with no 1/f and extended supply voltage range. The LMP2021/LMP2022 offer on chip EMI suppression circuitry which greatly enhances the performance of these precision amplifiers in the presence of radio frequency signals and other disturbances.

The LMP2021/LMP2022 utilize proprietary techniques to measure and continuously correct the input offset error voltage. The LMP2021/LMP2022 have a DC input offset voltage with a maximum value of  $\pm 5 \ \mu$ V and an input offset voltage drift maximum value of  $0.02 \ \mu$ V/°C. The input voltage noise of the LMP2021/LMP2022 is less than 11 nV/ $\ Hz$  at a voltage gain of 1000 V/V and has no flicker noise component. This makes the LMP2021/LMP2022 ideal for high accuracy, low frequency applications where lots of amplification is needed and the input signal has a very small amplitude.

The proprietary input offset correction circuitry enables the LMP2021/LMP2022 to have superior CMRR and PSRR performances. The combination of an open loop voltage gain of 160 dB, CMRR of 142 dB, PSRR of 130 dB, along with the ultra low input offset voltage of only –0.4  $\mu$ V, input offset voltage drift of only –0.004  $\mu$ V/°C, and input voltage noise of only 260 nV<sub>PP</sub> at 0.1 Hz to 10 Hz make the LMP2021/LMP2022 great choices for high gain transducer amplifiers, ADC buffer amplifiers, DAC I-V conversion, and other applications requiring precision and long-term stability. Other features are rail-to-rail output, low supply current of 1.1 mA per amplifier, and a gain-bandwidth product of 5 MHz.

The LMP2021/LMP2022 have an extended supply voltage range of 2.2V to 5.5V, making them ideal for battery operated portable applications. The LMP2021 is offered in 5-pin SOT-23 and 8-pin SOIC packages. The LMP2022 is offered in 8-pin MSOP and 8-Pin SOIC packages.

#### **EMI SUPPRESSION**

The near-ubiquity of cellular, bluetooth, and Wi-Fi signals and the rapid rise of sensing systems incorporating wireless radios make electromagnetic interference (EMI) an evermore important design consideration for precision signal paths. Though RF signals lie outside the op amp band, RF carrier switching can modulate the DC offset of the op amp. Also some common RF modulation schemes can induce downconverted components. The added DC offset and the induced signals are amplified with the signal of interest and thus corrupt the measurement. The LMP2021/LMP2022 use on chip filters to reject these unwanted RF signals at the inputs and power supply pins; thereby preserving the integrity of the precision signal path.

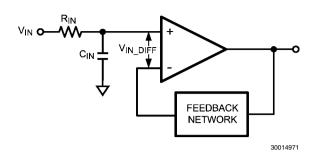

Twisted pair cabling and the active front-end's common-mode rejection provide immunity against low frequency noise (i.e. 60 Hz or 50 Hz mains) but are ineffective against RF interference. *Figure 12* displays this. Even a few centimeters of PCB trace and wiring for sensors located close to the amplifier can pick up significant 1 GHz RF. The integrated EMI filters of LMP2021/LMP2022 reduce or eliminate external shielding and filtering requirements, thereby increasing system robustness. A larger EMIRR means more rejection of the RF interference. For more information on EMIRR, please refer to AN-1698.

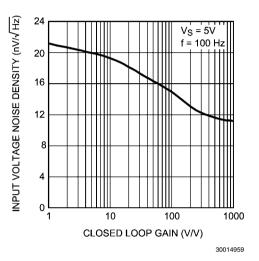

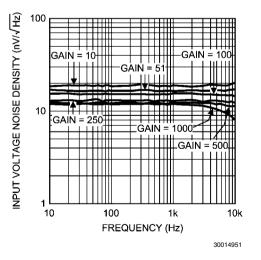

#### INPUT VOLTAGE NOISE

The input voltage noise density of the LMP2021/LMP2022 has no 1/f corner, and its value depends on the feedback network used. This feature of the LMP2021/LMP2022 differentiates this family from other products currently available from other vendors. In particular, the input voltage noise density decreases as the closed loop voltage gain of the LMP2021/LMP2022 increases. The input voltage noise of the LMP2021/LMP2022 is less than 11 nV/ $\sqrt{Hz}$  when the closed loop voltage gain of the op amp is 1000. Higher voltage gains are required for smaller input signals. When the input signal is smaller, a lower input voltage noise is quite advantageous and increases the signal to noise ratio.

*Figure 1* shows the input voltage noise of the LMP2021/ LMP2022 as the closed loop gain increases.

# FIGURE 1. Input Voltage Noise Density decreases with Gain

*Figure 2* shows the input voltage noise density does not have the 1/f component.

FIGURE 2. Input Voltage Noise Density with no 1/f

With smaller and smaller input signals and high precision applications with lower error budget, the reduced input voltage noise and no 1/f noise allow more flexibility in circuit design.

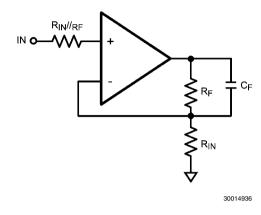

#### ACHIEVING LOWER NOISE WITH FILTERING

The low input voltage noise of the LMP2021/LMP2022, and no 1/f noise make these suitable for many applications with noise sensitive designs. Simple filtering can be done on the LMP2021/LMP2022 to remove high frequency noise. *Figure 3* shows a simple circuit that achieves this.

In *Figure 3*  $C_F$  and the corner frequency of the filter resulting from  $C_F$  and  $R_F$  will reduce the total noise.

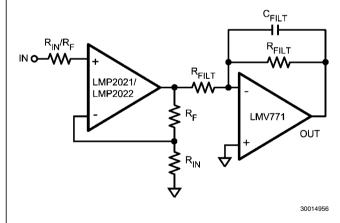

#### FIGURE 3. Noise Reducing Filter for Lower Gains

In order to achieve lower noise floors for even more noise stringent applications, a simple filter can be added to the op amp's output after the amplification stage. *Figure 4* shows the schematic of a simple circuit which achieves this objective. Low noise amplifiers such as the LMV771 can be used to create a single pole low pass filter on the output of the LMP2021/LMP2022. The noise performance of the filtering amplifier, LMV771 in this circuit, will not be dominant as the input signal on LMP2021/LMP2022 has already been significantly gained up and as a result the effect of the input voltage noise of the LMV771 is effectively not noticeable.

#### FIGURE 4. Enhanced Filter to Further Reduce Noise at Higher Gains

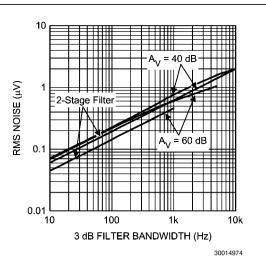

Using the circuit in *Figure 4* has the advantage of removing the non-linear filter bandwidth dependency which is seen when the circuit in *Figure 3* is used. The difference in noise performance of the circuits in *Figures 3*, 4 becomes apparent only at higher gains. At voltage gains of 10 V/V or less, there is no difference between the noise performance of the two circuits.

FIGURE 5. RMS Input Referred Noise vs. Frequency

*Figure 5* shows the total input referred noise vs. 3 dB corner of both filters of *Figure 3* and *Figure 4* at gains of 100V/V and 1000V/V. For these measurements and using *Figure 3*'s circuit,  $R_F = 49.7 \ k\Omega$  and  $R_{\rm IN} = 497\Omega$ . Value of  $C_F$  has been changed to achieve the desired 3 dB filter corner frequency. In the case of *Figure 4*'s circuit,  $R_F = 49.7 \ k\Omega$  and  $R_{\rm IN} =$  $497\Omega$ ,  $R_{\rm FILT} = 49.7 \ k\Omega$ , and  $C_{\rm FILT}$  has been changed to achieve the desired 3 dB filter corner frequency. *Figure 5* compares the RMS noise of these two circuits. As *Figure 5* shows, the RMS noise measured the circuit in *Figure 4* has lower values and also depicts a more linear shape.

#### DIGITAL ACQUISITION SYSTEMS

High resolution ADC's with 16-bits to 24-bits of resolution can be limited by the noise of the amplifier driving them. The circuit configuration, the value of the resistors used and the source impedance seen by the amplifier can affect the noise of the amplifier. The total noise at the output of the amplifier can be dominated by one of several sources of noises such as: white noise or broad band noise, 1/f noise, thermal noise, and current noise. In low frequency applications such as medical instrumentation, the source impedance is generally low enough that the current noise coupled into it does not impact the total noise significantly. However, as the 1/f or flicker noise is paramount to many application, the use of an auto correcting stabilized amplifier like the LMP2021/LMP2022 reduces the total noise.

Table 1: RMS Input Noise Performance summarizes the input and output referred RMS noise values for the LMP2021/ LMP2022 compared to that of Competitor A. As described in previous sections, the outstanding noise performance of the LMP2021/LMP2022 can be even further improved by adding a simple low pass filter following the amplification stage.

The use of an additional filter, as shown in *Figure 4* benefits applications with higher gain. For this reason, at a gain of 10, only the results of circuit in *Figure 3* are shown. The RMS input noise of the LMP2021/LMP2022 are compared with Competitor A's input noise performance. Competitor A's RMS input noise behaves the same with or without an additional filter.

| i                 |                               |                      |                 |              |  |  |

|-------------------|-------------------------------|----------------------|-----------------|--------------|--|--|

| Amplifier<br>Gain | Question                      | RMS Input Noise (nV) |                 |              |  |  |

|                   | Bandwidth                     | LMP2021/             | Competitor<br>A |              |  |  |

| (V/V)             | V/V) Requirement<br>(Hz) Figu |                      | Figure 4        | Figures 4, 3 |  |  |

|                   | (112)                         | Circuit              | Circuit         | Circuit      |  |  |

| 10                | 100                           | 229                  | *               | 300          |  |  |

| 10                | 1000                          | 763                  | *               | 1030         |  |  |

| 100               | 100 100                       |                      | 196             | 300          |  |  |

| 100               | 1000                          | 763                  | 621             | 1030         |  |  |

|                   | 10                            | 71                   | 46              | 95           |  |  |

| 1000              | 100                           | 158                  | 146             | 300          |  |  |

|                   | 1000                          | 608                  | 462             | 1030         |  |  |

$^{\ast}$  No significant difference in Noise measurements at  $A_{V}=10V/V$

#### **INPUT BIAS CURRENT**

The bias current of the LMP2021/LMP2022 behaves differently than a conventional amplifier due to the dynamic tran-

sient currents created on the input of an auto-zero circuit. The input bias current is affected by the charge and discharge current of the input auto-zero circuit. The amount of current sunk or sourced from that stage is dependent on the combination of input impedance (resistance and capacitance), as well as the balance and matching of these impedances across the two inputs. This current, integrated in the auto-zero circuit, causes a shift in the apparent "bias current". Because of this, there is an apparent "bias current vs. input impedance" interaction. In the LMP2021/LMP2022 for an input resistive impedance of 1 G $\Omega$ , the shift in input bias current can be up to 40 pA. This input bias shift is caused by varying the input's capacitive impedance. Since the input bias current is dependent on the input impedance, it is difficult to estimate what the actual bias current is without knowing the end circuit and associated capacitive strays.

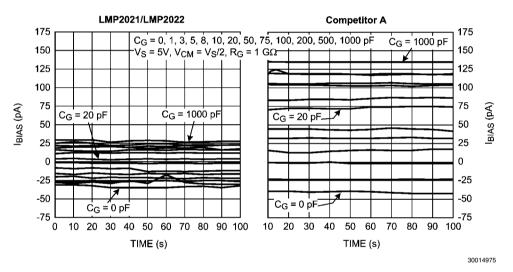

*Figure 6* shows the input bias current of the LMP2021/ LMP2022 and that of another commercially available amplifier from a competitor. As it can be seen, the shift in LMP2021/ LMP2022 bias current is much lower than that of other chopper style or auto zero amplifiers available from other vendors.

FIGURE 6. Input Bias Current of LMP2021/LMP2022 is lower than Competitor A

#### LOWERING THE INPUT BIAS CURRENT

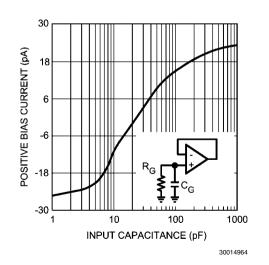

As mentioned in the INPUT BIAS CURRENT section, the input bias current of an auto zero amplifier such as the LMP2021/LMP2022 varies with input impedance and feedback impedance. Once the value of a certain input resistance, i.e. sensor resistance, is known, it is possible to optimize the input bias current for this fixed input resistance by choosing the capacitance value that minimizes that current. Figure 7 shows the input bias current vs. input impedance of the LMP2021/LMP2022. The value of  $\mathrm{R}_{\mathrm{G}}$  or input resistance in this test is 1 G $\Omega$ . When this value of input resistance is used, and when a parallel capacitance of 22 pF is placed on the circuit, the resulting input bias current is nearly 0 pA. Figure 7 can be used to extrapolate capacitor values for other sensor resistances. For this purpose, the total impedance seen by the input of the LMP2021/LMP2022 needs to be calculated based on Figure 7. By knowing the value of R<sub>G</sub>, one can calculate the corresponding C<sub>G</sub> which minimizes the noninverting input bias current, positive bias current, value.

FIGURE 7. Input Bias Current vs.  $C_G$  with  $R_G = 1 G\Omega$

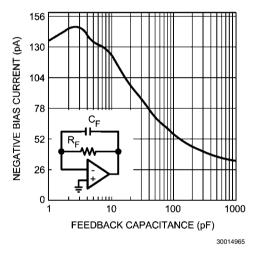

In a typical I-V converter, the output voltage will be the sum of DC offset plus bias current and the applied signal through the feedback resistor. In a conventional input stage, the inverting input's capacitance has very little effect on the circuit. This effect is generally on settling time and the dielectric soakage time and can be ignored. In auto zero amplifiers, the input capacitance effect will add another term to the output. This additional term means that the baseline reading on the output will be dependent on the input capacitance. The term input capacitance for this purpose includes circuit stravs and any input cable capacitances. There is a slight variation in the capacitive offset as the duty cycle and amplitude of the pulses vary from part to part, depending on the correction at the time. The lowest input current will be obtained when the impedances, both resistive and capacitive, are matched between the inputs. By balancing the input capacitances, the effect can be minimized. A simple way to balance the input impedance is adding a capacitance in parallel to the feedback resistance. The addition of this feedback capacitance reduces the bias current and increases the stability of the operational amplifier. Figure 8 shows the input bias current of the LMP2021/LMP2022 when  $R_F$  is set to 1 G $\Omega$ . As it can be seen from Figure 8, choosing the optimum value of C<sub>F</sub> will help reducing the input bias current.

#### FIGURE 8. Input Bias Current vs. $C_F$ with $R_F = 1 G\Omega$

The effect of bias current on a circuit can be estimated with the following:

$$A_V * I_{BIAS+} * Z_S - I_{BIAS-} * Z_F$$

Where  $A_V$  is the closed loop gain of the system and  $I_{BIAS+}$  and  $I_{BIAS-}$  denote the positive and negative bias current, respectively. It is common to show the average of these bias currents in product datasheets. If  $I_{BIAS+}$  and  $I_{BIAS-}$  are not individually specified, use the  $I_{BIAS}$  value provided in datasheet graphs or tables for this calculation.

For the application circuit shown in *Figure 12*, the LMP2022 amplifiers each have a gain of 18. With a sensor impedance of  $500\Omega$  for the bridge, and using the above equation, the total error due to the bias current on the outputs of the LMP2022 amplifier will be less than 200 nV.

#### SENSOR IMPEDANCE

The sensor resistance, or the resistance connected to the inputs of the LMP2021/LMP2022, contributes to the total impedance seen by the auto correcting input stage.

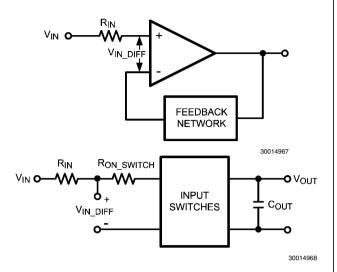

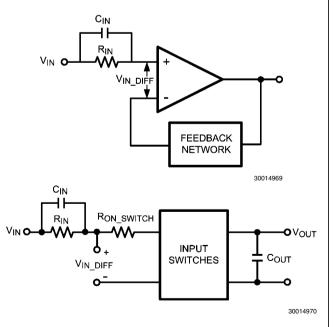

#### FIGURE 9. AUTO CORRECTING INPUT STAGE MODEL

As shown in *Figure 9*, the sum of R<sub>IN</sub> and R<sub>ON-SWITCH</sub> will form a low pass filter with C<sub>OUT</sub> during correction cycles. As R<sub>IN</sub> increases, the time constant of this filter increases, resulting in a slower output signal which could have the effect of reducing the open loop gain, A<sub>VOL</sub>, of the LMP2021/LMP2022. In order to prevent this reduction in A<sub>VOL</sub> in presence of high impedance sensors or other high resistances connected to the input of the LMP2021/LMP2022, a capacitor can be placed in parallel to this input resistance. This is shown in *Figure 10*

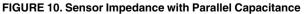

$\rm C_{IN}$  in *Figure 10* adds a zero to the low pass filter and hence eliminating the reduction in A<sub>VOL</sub> of the LMP2021/LMP2022. An alternative circuit to achieve this is shown in *Figure 11*.

#### FIGURE 11. Alternative Sensor Impedance Circuit

#### TRANSIENT RESPONSE TO FAST INPUTS

On chip continuous auto zero correction circuitry eliminates the 1/f noise and significantly reduces the offset voltage and offset voltage drift; all of which are very low frequency events. For slow changing sensor signals this correction is transparent. For excitations which may otherwise cause the output to swing faster than 40 mV/ $\mu$ s, there are additional considerations which can be viewed two perspectives: for sine waves and for steps.

For sinusoidal inputs, when the output is swinging rail-to-rail on  $\pm 2.5V$  supplies, the auto zero circuitry will introduce distortions above 2.55 kHz. For smaller output swings, higher frequencies can be amplified without the auto zero slew limitation as shown in table below. Signals above 20 kHz, are not affected, though normally, closed loop bandwidth should be kept below 20 kHz so as to avoid aliasing from the auto zero circuit.

| V <sub>OUT-PEAK</sub> (V) | f <sub>MAX-SINE WAVE</sub> (kHz) |

|---------------------------|----------------------------------|

| 0.32                      | 20                               |

| 1                         | 6.3                              |

| 2.5                       | 2.5                              |

For step-like inputs, such as those arising from disturbances to a sensing system, the auto zero slew rate limitation manifests itself as an extended ramping and settling time, lasting ~100  $\mu$ s.

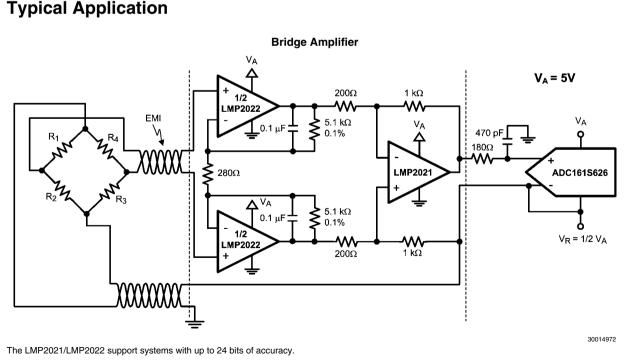

#### DIFFERENTIAL BRIDGE SENSOR

Bridge sensors are used in a variety of applications such as pressure sensors and weigh scales. Bridge sensors typically have a very small differential output signal. This very small signal needs to be accurately amplified before it can be fed into an ADC. As discussed in the previous sections, the accuracy of the op amp used as the ADC driver is essential to maintaining total system accuracy.

The high DC performance of the LMP2021/LMP2022 make these amplifiers ideal choices for use with a bridge sensor. The LMP2021/LMP2022 have very low input offset voltage and very low input offset voltage drift. The open loop gain of the LMP2021/LMP2022 is 160 dB.

The on chip EMI rejection filters available on the LMP2021/ LMP2022 help remove the EMI interference introduced to the signal and hence improve the overall system performance. The circuit in Figure 12 shows a signal path solution for a typical bridge sensor using the LMP2021/LMP2022. Bridge sensors are created by replacing at least one, and up to all four, of the resistors in a typical bridge with a sensor whose resistance varies in response to an external stimulus. Using four sensors has the advantage of increasing output dynamic range. Typical output voltage of one resistive pressure sensor is 2 mV per 1V of bridge excitation voltage. Using four sensors, the output of the bridge is 8 mV per 1V. The bridge voltage is this system is chosen to be 1/2 of the analog supply voltage and equal to the reference voltage of the AD-C161S626, 2.5V. This excitation voltage results in 2.5V \* 8 mV = 20 mV of differential output signal on the bridge. This 20 mV signal must be accurately amplified by the amplifier to best match the dynamic input range of the ADC. This is done by using one LMP2022 and one LMP2021 in front of the AD-C161S626. The gaining of this 20 mV signal is achieved in 2 stages and through an instrumentation amplifier. The LMP2022 in Figure 12 amplifies each side of the differential output of the bridge sensor by a gain 18. Bridge sensor measurements are usually done up to 10s of Hz. Placing a 300 Hz filter on the LMP2022 helps removing the higher frequency noise from this circuit. This filter is created by placing two capacitors in the feedback path of the LMP2022 amplifiers. Using the LMP2022 with a gain of 18 reduces the input referred voltage noise of the op amps and the system as a result. Also, this gain allows direct filtering of the signal on the LMP2022 without compromising noise performance. The differential output of the two amplifiers in the LMP2022 are then fed into a LMP2021 configured as a difference amplifier. This stage has a gain of 5, with a total system having a gain of (18\*2+1)\*5 = 185. The LMP2021 has an outstanding CMRR value of 139. This impressive CMRR improves system performance by removing the common mode signal introduced by the bridge. With an overall gain of 185, the 20 mV differential input signal is gained up to 3.7V. This utilizes the amplifiers output swing as well as the ADC's input dynamic range.

This amplified signal is then fed into the ADC161S626. The ADC161S626 is a 16-bit, 50 kSPS to 250 kSPS 5V ADC. In order to utilize the maximum number of bits of the AD-C161S626 in this configuration, a 2.5V reference voltage is used. This 2.5V reference is also used to power the bridge sensor and the inverting input of the ADC. Using the same voltage source for these three points helps reducing the total system error by eliminating error due to source variations.

With this system, the output signal of the bridge sensor which can be up to 20 mV is accurately gained to the full scale of the ADC and then digitized for further processing. The LMP2021/LMP2022 introduced minimal error to the system and improved the signal quality by removing common model signals and high frequency noise.

### Physical Dimensions inches (millimeters) unless otherwise noted

8-Pin MSOP NS Package Number MUA08A LMP2021/LMP2022

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | De                      | sign Support                   |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools          | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes               | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs       | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                 | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards             | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging               | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance        | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors            | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support        | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy        | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions               | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | Solar Magic®            | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | Analog University®      | www.national.com/AU            |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com